В среду компания Samsung Electronics провела конференцию, в ходе которой рассказала о планах по освоению новых технологических процессов. Подчеркнём, что это уже не слухи и утечки, а вполне обоснованная «дорожная карта». Фактически руководство к действию. Главным для нас и для отрасли стало сообщение, что рисковое производство с нормами 4 нм компания Samsung собирается начать в 2020 году.

wsj.com

Для выпуска 4-нм решений будет использоваться EUV-проекция с длиной волны 13,5 нм. В настоящий момент компания работает с экспериментальными EUV-сканерами, и она убедилась, что опытное оборудование вполне справляется с нагрузкой в виде 1000 300-мм пластин (подложек) в сутки. Для оправданного коммерческого производства требуется производительность 1500 пластин в сутки, что будет достижимо после появления сканеров с излучателями мощностью 250 Вт. В компании уверены, что эта проблема решится в ближайшем будущем. Тем самым Samsung утверждает, что в производстве она начнёт использовать EUV-сканеры уже в 2018 году для массового выпуска чипов с использованием второго поколения 7-нм техпроцесса (LPP). Она станет первой в мире компанией, которая перейдёт на EUV-литографию.

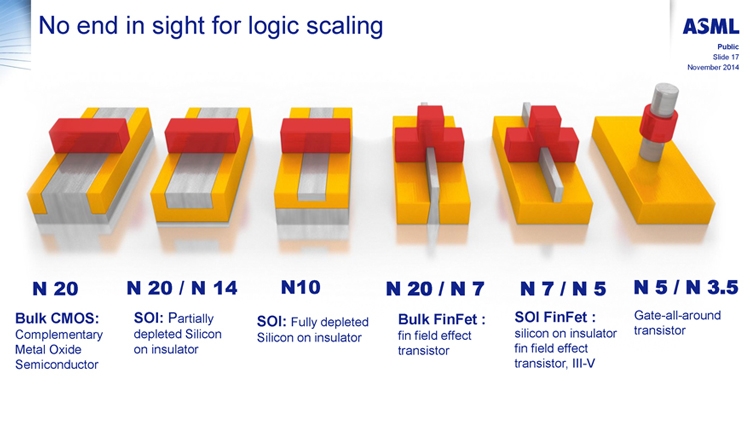

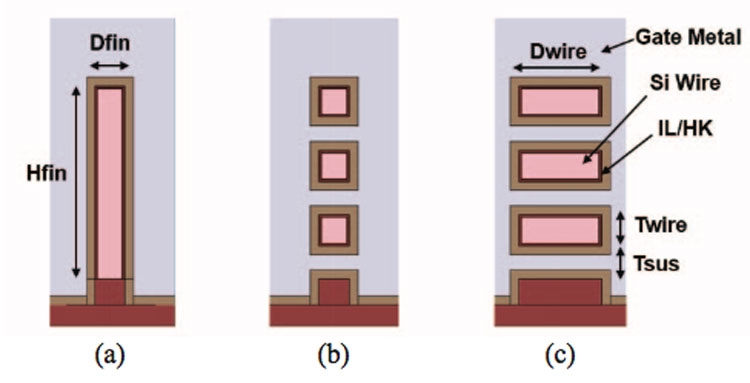

Варианты архитектуры затворов и каналов транзисторов (ASML)

Следует сказать, что для 4-нм техпроцесса транзисторы изменят свою архитектуру. Это будет, как выразились в Samsung, архитектура «post FinFET». Сегодня канал FinFET транзистора под затвором представляет собой монолитную вертикальную конструкцию «плавник» или содержит несколько рёбер для повышения уровня пропускаемого через транзистор тока. В дальнейшем канал будет со всех сторон окружён затвором — это так называемая структура gate-all-around FET (GAAFET). В такой структуре каналы выполнены как нанопровода или наностраницы. Транзисторы Samsung с началом выпуска 4-нм решений будут использовать одну из версий каналов в виде наностраниц. В компании называют это транзисторами multi-bridge channel FET (MBCFET) или вертикальная структура со многими перемычками.

Каналы транзисторов превратятся в «перемычки» из нанопроводов и наностраниц (изображение IBM)

До 2020 года компания последовательно освоит техпроцесс с нормами 8 нм (LPP), что произойдёт в текущем году, и техпроцесс с нормами 7 нм (LPP), о котором выше уже сказано. Следующими техпроцессами станут 6-нм и 5-нм техпроцессы LPP. Техпроцесс с нормами 6 нм компания планирует внедрить в производство в 2019 году. При всём при этом Samsung уверена, что 10-нм техпроцесс станет «решением на года» и будет многие годы самым популярным среди разработчиков техпроцессом.

Президент полупроводникового бизнеса Samsung Ким Ки-нам (Kim Ki-nam) (Фото EE Times)

Наконец, компания подтвердила намерение начать в 2019 году выпуск полупроводников с нормами 18 нм на пластинах FD-SOI. Сегодня на пластинах с изолятором из полностью обеднённого кремния компания выпускает 28-нм чипы. Переход с этого техпроцесса на 18-нм обещает на 40 % снизить потребление решений и на 20 % увеличить производительность, попутно сэкономив на площади кристалла.

Источник: 3DNews