Замедление темпов перехода на новые технологические нормы для выпуска полупроводников заставляет производителей и разработчиков искать иные средства для увеличения сложности и функциональности решений. Застой уже на горизонте. Техпроцесс с нормами 5 нм обещает родиться в муках и прийти надолго. Один из способов обойти это ограничение заключается в возможности упаковать в один корпус микросхемы несколько кристаллов, чтобы внешне всё работало как один чип с минимальными задержками. При этом кристаллы должны быть расположены как можно ближе друг к другу.

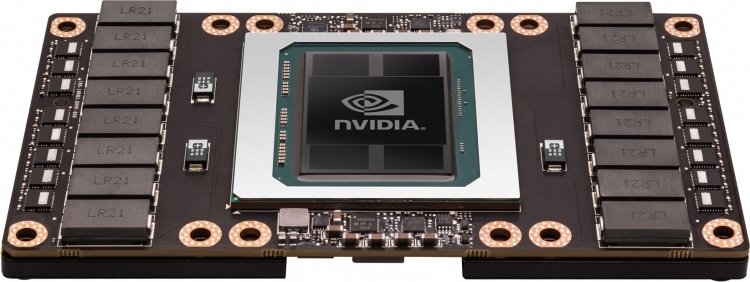

NVIDIA Tesla P100 (пример упаковки TSMC CoWoS, GPU и HBM)

Другое требование — соединяющие кристаллы проводники должны быть скрыты внутри кристаллов, а не так, как раньше — в виде сотен тоненьких проводников, которые оплетают кристаллы со всех сторон и уходят «корнями» в контактную площадку вокруг основания кристаллов. Сегодня для этого используются так называемые сквозные соединения TSVs (каналы металлизации), диаметр которых снизился с сотен до единиц микрон. С использованием TSVs-соединений научились выпускать память HBM, однако логику пока не упаковывают в 3D. Для этого всё ещё используется упаковка 2.5D. С помощью упаковки 2.5D выпускаются GPU AMD с памятью HBM (упаковка компаний Amkor Technology и Advanced Semiconductor Engineering) и GPU NVIDIA с памятью HBM2 (упаковывает TSMC). Данный способ предполагает использование кремниевого моста, что значительно увеличивает площадь и объём решения. Какое же это 3D?

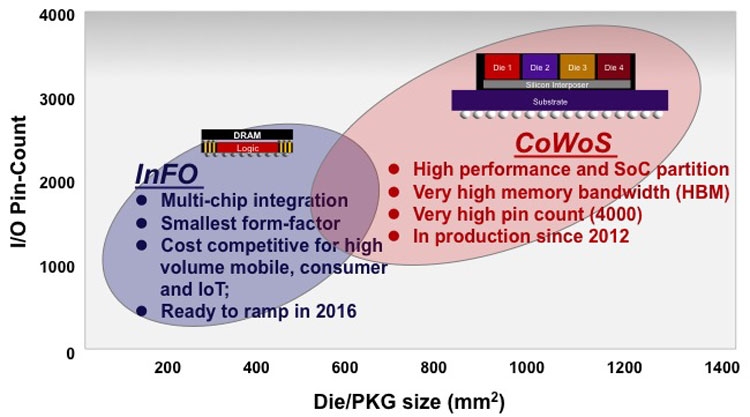

Два актуальных варианта 2.5D упаковки кристаллов на заводе TSMC

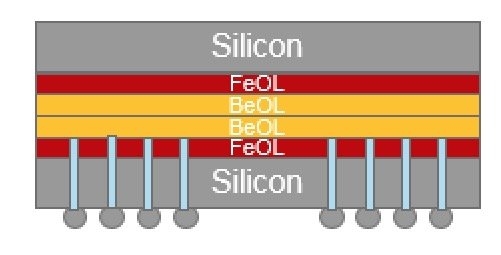

Уточним, 2.5D-упаковка TSMC называется CoWoS (Chip on Wafer on Substrate). Использовать CoWoS компания начала в 2012 году для упаковки 28-нм решений. «Настоящее 3D» компания обещает реализовать в упаковке WoW (wafer-on-wafer). Технология WoW подразумевает монтаж кристаллов непосредственно друг на друга либо со стороны элементов, либо со стороны пластин. В любом случае в месте стыка должны быть созданы группы мельчайших контактов, которые надо будет совместить с величайшей точностью. Технология допускает монтаж двух или трёх кристаллов. В последнем случае, как нетрудно догадаться, вопрос отвода тепла от среднего уровня будет стоять довольно остро.

Пример упаковки Wafer on Wafer (Cadence)

Кроме упаковки WoW компания предложила ряд других вариантов, часть из которых является недорогой альтернативой CoWoS. Так, TSMC расширила список технологий InFO (Integrated Fan Out). Если CoWoS и WoW ориентированы на высокопроизводительные решения (за счёт качественных соединений моста, либо в случае прямого контакта), то InFO — это просто залитые компаундом контактные группы и кристалл или кристаллы. По технологии InFO, например, с 2016 года выпускаются SoC для Apple и для других разработчиков SoC для смартфонов. Эта технология позволяет разместить над процессором модуль памяти и сделать конструкцию компактнее и тоньше (моста-то нет). С текущего года технология InFO получит четыре разновидности: Info-MS, InFO-oS, MUST (multi-stacking) и InFO-AIP.

Технологии Info-MS и InFO-oS помогут упаковать вместе с SoC память HBM и DRAM. Шаг контактов снижен с 5 до 2 мкм, а горизонтальное расположение кристаллов ещё немного снизит стоимость упаковки. Технология MUST поможет упаковать до трёх кристаллов в столбик (друг на друге), а технология InFO-AIP — это упаковка для радиокомпонентов с антенной сверху. Последний подход обещает на 10 % уменьшить площадь решения и на 40 % увеличить усиление антенны. Ожидается, что такие упаковки будут востребованы для выпуска решений для сетей 5G.

Источник: 3DNews