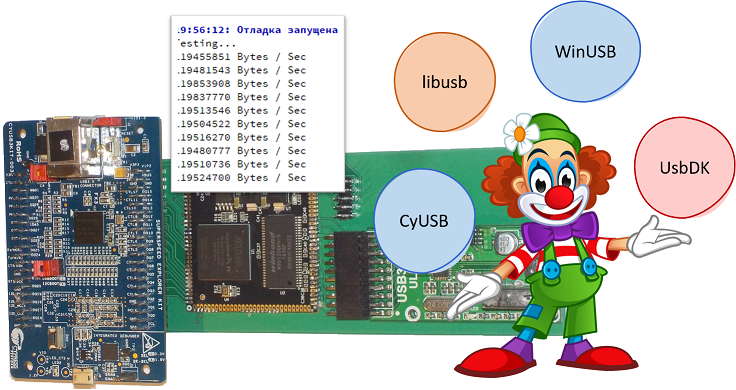

Учимся работать с USB-устройством и испытываем систему, сделанную на базе контроллера FX3

В двух предыдущих статьях мы сделали USB 3.0 систему на базе контроллера FX3. Пришла пора научиться работать с нею из своих программ для PC. Ну, и попутно понять, насколько получившаяся система пригодна для практического применения. Действительно ли ширины канала хватает…

Читать дальше

![[Перевод] Запуск Unix-подобной ОС на самодельном CPU с помощью самодельного компилятора C [Перевод] Запуск Unix-подобной ОС на самодельном CPU с помощью самодельного компилятора C](https://habrastorage.org/getpro/habr/post_images/cbc/440/fab/cbc440fabc25314f825bce5f9865986c.png)

![[Из песочницы] The Snake game for FPGA Cyclone IV (with VGA & SPI joystick) [Из песочницы] The Snake game for FPGA Cyclone IV (with VGA & SPI joystick)](https://github.com/Sitiritis/SnakeGame_FPGA/blob/master/text/img/gameplay.gif?raw=true)

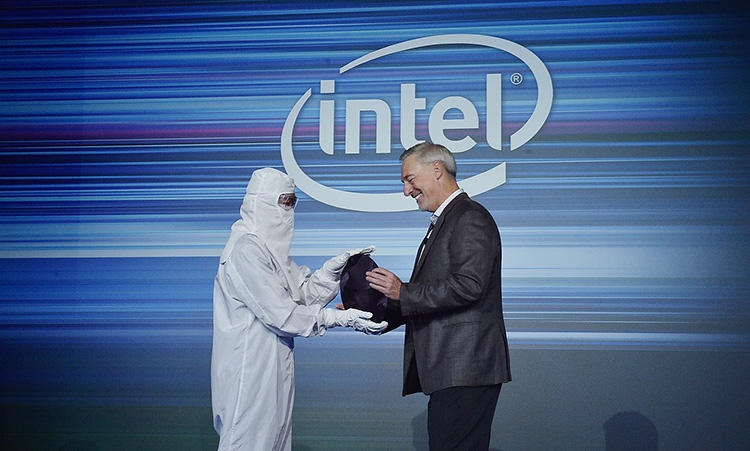

![[Перевод] Как искусственный интеллект меняет рынок чипов [Перевод] Как искусственный интеллект меняет рынок чипов](https://habrastorage.org/getpro/geektimes/post_images/cb9/42c/98d/cb942c98d6a2ea40dd008c12ac8e59fc.jpg)