До мая 2016 года у полупроводникового подразделения компании Samsung Electronics не было особенной необходимости работать на публику, например, делиться планами и тонкостями грядущих технологических процессов. После означенной выше даты Samsung выделила из полупроводникового подразделения группу для контрактного производства чипов и оказалась вовлечена в увлекательный процесс популяризации фирменных техпроцессов. Компания TSMC делает это давно и со вкусом, к примеру, регулярно и в красках расписывая, как она начнёт выпускать 5-нм чипы и даже 3-нм. Что же, Samsung решила взять опыт конкурента на вооружение и сегодня удачно его применила.

wsj.com

В Санта-Кларе на домашней конференции Samsung Foundry Forum (SFF) 2018 USA представители южнокорейского производителя рассказали о будущих техпроцессах с нормами 7 нм, 5 нм, 4 нм и 3 нм. Людям необходимы всё более компактные и мощные мобильные решения с постоянным подключением к Сети. Поэтому в компании Samsung трепетно относятся к важности непрерывного внедрения новейших техпроцессов, чтобы удержать баланс между потреблением и производительностью.

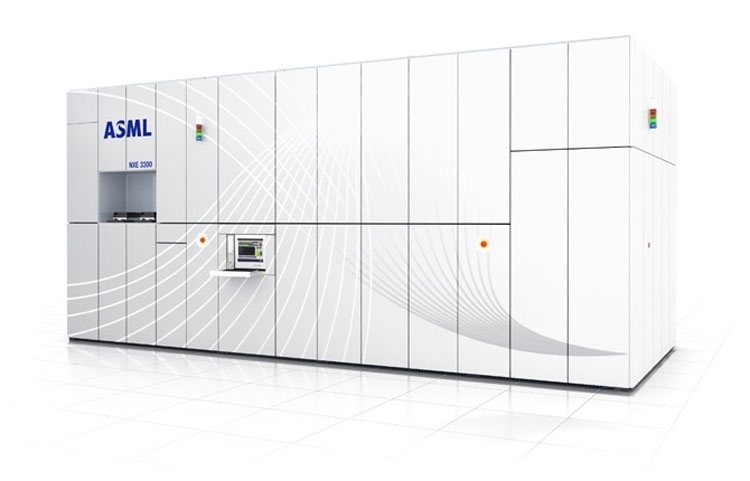

Так, техпроцесс 7LPP (7nm Low Power Plus) будет готов к выпуску решений во втором полугодии текущего года. Правда, полный комплект IP-блоков в виде готовых для применения разработчиками решений для техпроцесса 7LPP будет подготовлен лишь в первой половине 2019 года. Это отсрочит появление массовых 7-нм чипов, но не отпугнёт тех, которые готовы самостоятельно разрабатывать схемотехнику для скорейшего выпуска 7-нм продукции. Например, компания Qualcomm готова выпускать 5G-чипы с использованием техпроцесса Samsung 7LPP. Это, кстати, будет первый в индустрии техпроцесс, который станет частично использовать сканеры диапазона EUV.

Первый коммерческий сканер ASML для EUV-литографии (NXE:3300B)

Следующим техпроцессом, который Samsung намерена внедрить в производство в 2019 году, станет техпроцесс 5LPE (5nm Low Power Early). Отметим, для техпроцесса с нормами 7 нм нет «раннего» варианта типа 7LPE (Early). В компании сразу решили переходить к частичному использованию сканеров EUV. Поэтому техпроцесс 5LPE станет чем-то вроде развитой версии техпроцесса 7LPP, что позволит уменьшить площадь кристаллов и увеличить энергоэффективность решений. Подчеркнём, это всё ожидается в следующем году, когда TSMC будет только начинать использовать сканеры EUV для второго поколения своего 7-нм техпроцесса. Так что у Samsung очень агрессивный план по внедрению новых техпроцессов.

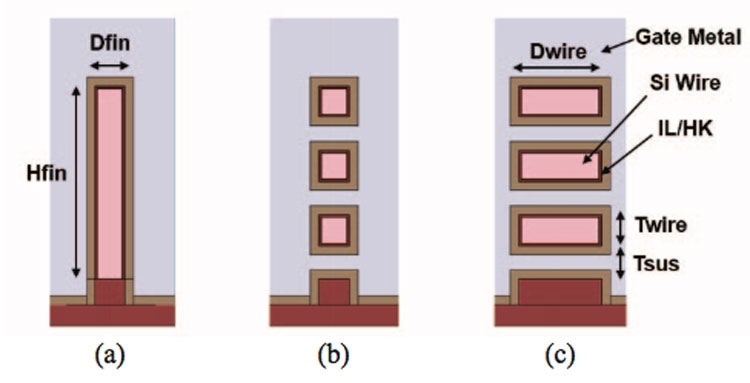

Каналы транзисторов превратятся в «перемычки» из нанопроводов и наностраниц (изображение IBM)

В 2020 году уже на основе внедрённого в производство техпроцесса 5LPE и с учётом всех выявленных недочётов компания Samsung планирует внедрить в производство техпроцессы 4LPE/LPP (4nm Low Power Early/Plus). Что интересно, решения с нормами 4 нм сохранят структуру вертикальных транзисторов FinFET, хотя ранее компания на этом этапе планировала перейти на кольцевые затворы. Очевидно, было принято решение не экспериментировать, а внедрять то, что пока ещё может работать. Техпроцесс 5LPP отсутствует в планах компании, а заменить его, по-видимому, решено 4-нм техпроцессом.

Реальное изображение транзисторов с затворами вокруг наностраниц (IBM, техпроцесс 5 нм)

Техпроцесс с нормами 3 нм и кольцевыми затворами Gate-All-Around в виде версий 3GAAE/GAAP (3nm Gate-All-Around Early/Plus) компания собирается внедрить в 2021 году. Кольцевые затворы будут окружать транзисторные каналы со всех сторон, что позволит удержать рабочие токи на заданном уровне, несмотря на сильно измельчавшие каналы и площади затворов. Уточним, Samsung выбрала в качестве затворов наностраницы, а не нанопровода. Проще говоря, кольцевые затворы в разрезе будут выглядеть как прямоугольники со скруглёнными краями. Подробные и ожидаемые характеристики транзисторов для всех указанных техпроцессов Samsung обещает обнародовать позже.

Источник: 3DNews