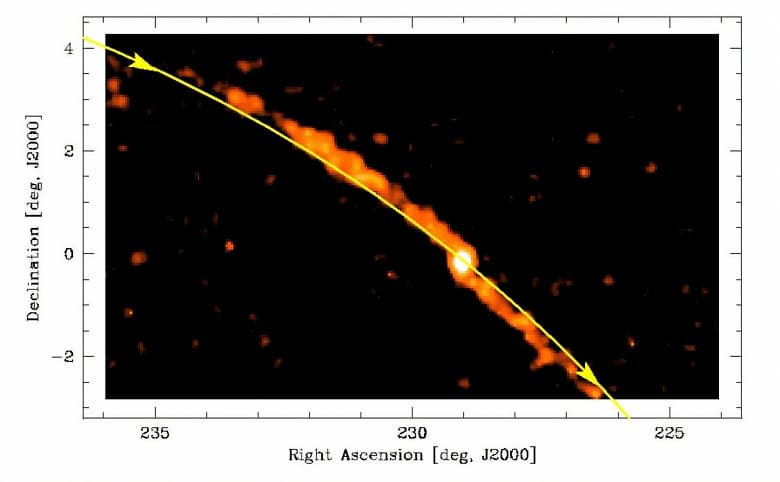

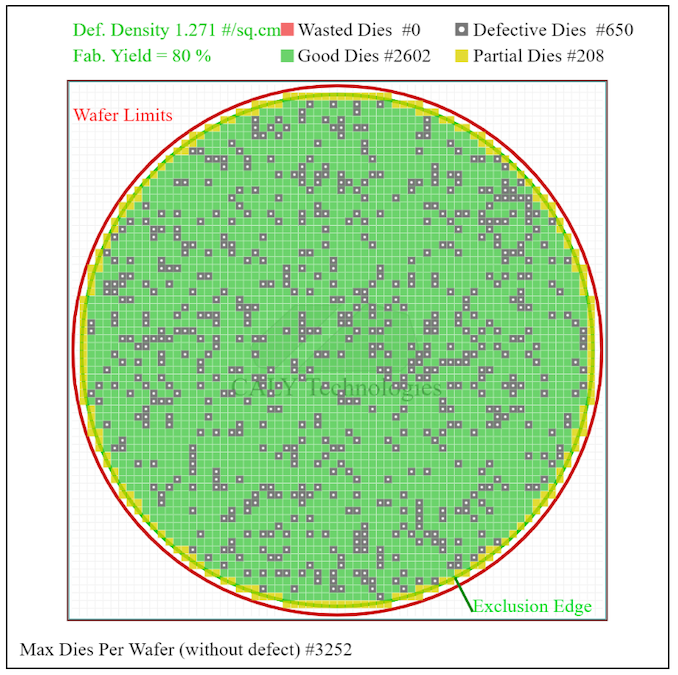

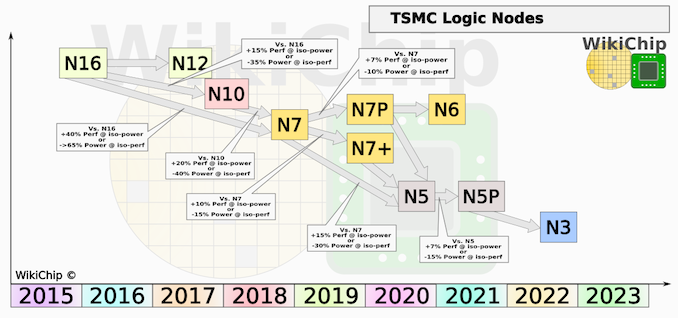

В станах конкурентов-лидеров по выпуску полупроводников чуть больше ясности, что подтверждено рисковым производством TSMC чипов с нормами 5 нм (на сегодняшний день уровень брака по таковому всего 20 % при норме 3-8 % для кристаллов площадью 17,92 мм2, для чиплетов размера AMD Zen 2 уровень брака будет больше ― до 60 %). Впрочем, до выпуска процессоров AMD с нормами 5 нм пройдёт ещё не менее полутора лет.

/ изображение с сайта AnandTech

В следующем году со второго квартала техпроцесс TSMC с нормами 5 нм будет использоваться для серийного выпуска SoC на ядрах ARM. В 2022 году TSMC приступит, очевидно, к рисковому выпуску 3-нм чипов (что бы ни значили эти нанометры), а через пару лет компания обещает начать выпуск 2-нм решений. Это будет в 2024-2025 году или на два-три года раньше, чем тот же самый техпроцесс внедрит Intel.

Для компании Samsung техпроцессы с нормами 5 нм и 4 нм станут эволюцией 7-нм техпроцесса, что будет выражено в небольшом постепенном сокращении шагов металлизации под такими элементами FinFET транзисторов, как каналы и затворы. В целом строение транзисторов (число рёбер) останется тем же, как и не изменится строение ячейки SRAM. К выпуску чипов с использованием 4-нм техпроцесса Samsung приступит в районе 2021 года. В том же году компания обещает начать рисковое производство с использованием 3-нм техпроцесса. А некоторые южнокорейские источники утверждают, что это может произойти уже в 2020 году, что выглядит маловероятным.

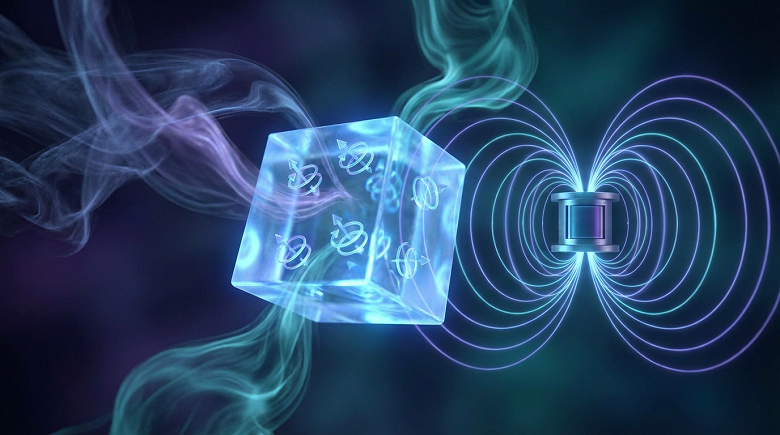

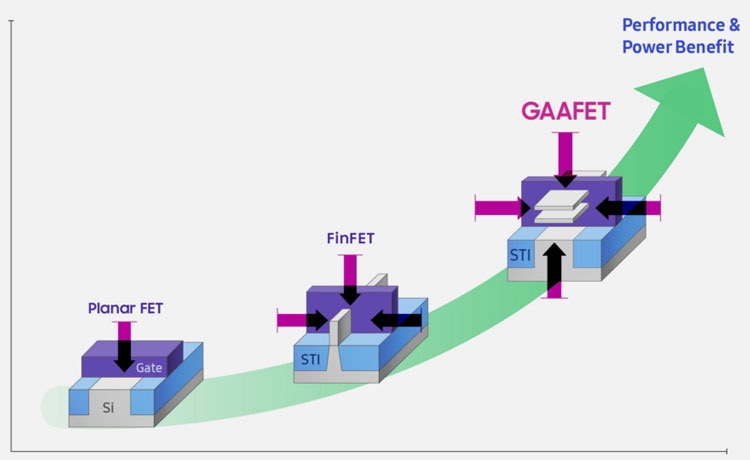

В данной заметке нас интересует то, что, вплоть до 4-нм техпроцесса Samsung и, очевидно, Intel и TSMC будут использовать FinFET транзисторы ― плавники высоких затворов, в которые врезаются и пронзают насквозь вертикальные гребни каналов. В таких транзисторах электромагнитное поле затвора проникает в каналы с трёх сторон, а два-три канала в каждом транзисторе в сумме обеспечивают необходимую для работы вентиля силу тока.

/ изображение Samsung

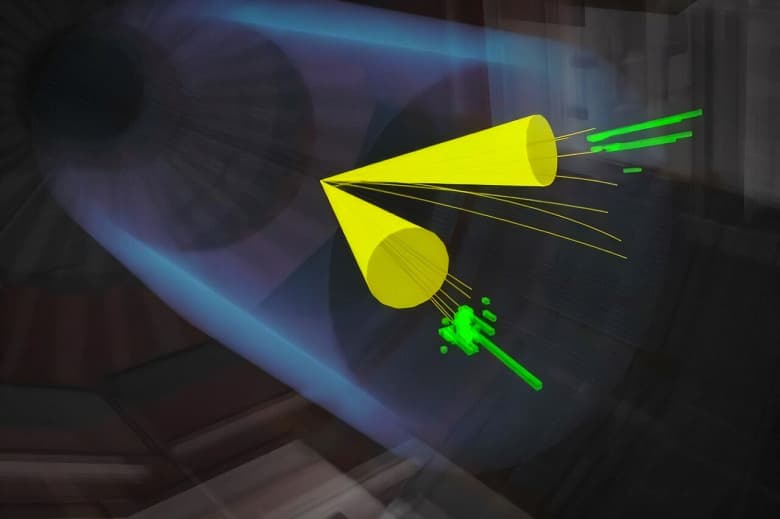

Начиная с 3-нм техпроцесса, Samsung поломает эту практику. Концепция FinFET перестанет работать в прежнем виде. Затворы транзисторов FinFET окажутся слишком малы и не смогут переключать транзисторы. Необходимость дальнейшего снижения напряжения питания транзисторов только усугубит это положение. Поэтому для 3-нм техпроцесса будет введён транзистор с кольцевым (окружающим) затвором GAA (Gate-All-Around).

/ изображение Samsung

В Samsung дали новому транзистору коммерческое имя MBCFET (Multi Bridge Channel FET). На практике это развитие идеи транзистора, созданного совместно исследователями IBM, Samsung и GlobalFoundries. Предполагалось, что подобный по строению транзистор будет задействован при переходе к техпроцессу с нормами 5 нм. Но реально эта вентильная структура появится в чипах только с началом 3-нм производства Samsung. Транзистор MBCFET будет представлять собой горизонтально расположенные друг над другом каналы в виде наностраниц, а не вертикальные гребни, как в FinFET. Характеристиками MBCFET транзисторов будет удобно управлять как за счёт варьирования числом страниц, расположенных друг над другом, так и с помощью изменения ширины страницы. Каждая страница ― это канал. Сумма этих переменных будет определять какой у нас транзистор: мощный и быстрый, или слабый, но малопотребляющий. Градаций будет больше двух ― от пяти до семи.

/ изображение Samsung

Самое интересное, ради чего затевалась эта заметка, что транзистор MBCFET может появиться только в рамках 3-нм техпроцесса, а техпроцесс с нормами 2 нм снова потребует изменений в строении транзистора. Такой новый транзистор под именем Forksheet предложил бельгийский исследовательский центр Imec. Впервые подробно о структуре транзистора с раздельными (нано)страницами представители Imec рассказали весной этого года на годовом мероприятии. Но баснями соловья не накормишь. Нам бы пощупать. Пощупать пока нельзя, но моделирование работы Forksheet-транзистора на TCAD бельгийцы провели, о чём сообщили три дня назад.

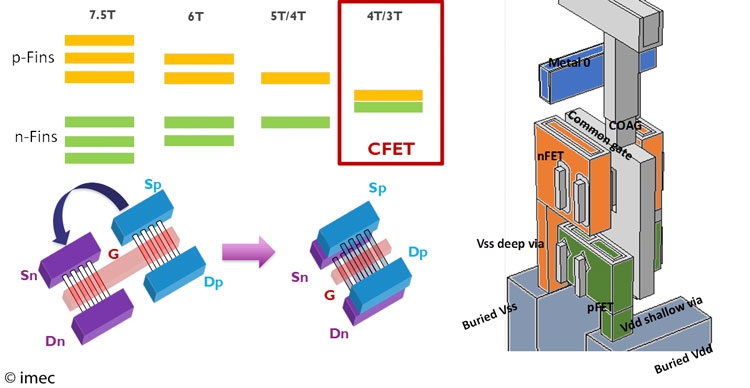

Перед тем, как рассмотреть полученные данные, поясним, что транзистор Forksheet представляет собой модификацию транзистора с наностраницами ― того самого MBCFET или Gate-All-Around, если абстрагироваться от терминов Samsung. В транзисторе Forksheet плавник вертикального затвора чуть шире, чем у MBCFET, но наностраницы транзисторных каналов расщеплены надвое и разделены слоем диэлектрика. Фактически один MBCFET-транзистор лёгким движением руки превращается в комплементарную транзисторную пару из транзисторов p- и n-типа. Предложенная структура разрушает серьёзный барьер в уплотнении транзисторов в виде сложности максимально сблизить p- и n-транзисторы и избежать при этом взаимного негативного влияния вентилей.

Очевидно, что предложенный подход увеличит плотность размещения транзисторов на кристалле, но моделирование показало, что улучшатся также производительность и энергопотребление. Переход на транзистор с раздельными страницами позволит уменьшить площадь кристалла до 20 %, а за счёт снижения паразитных ёмкостей и утечек производительность электронных приборов вырастет на величину до 10 %. Если не наращивать частоты, то можно снизить энергопотребление на величину до 24 %.

В запасе у Imec есть ещё одна технология, которая может ещё сильнее увеличить плотность размещения транзисторов. Она может быть применена как на этапе выпуска 3-нм чипов, так и с меньшими нормами производства. Идея заключается в том, чтобы комплементарную пару транзисторов изготавливать друг над другом. Эта нехитрая на первый взгляд операция обещает на 50 % уменьшить размеры как стандартной логической ячейки, так и ячейки SRAM. На этом хорошо проработанные и частично испытанные на моделях идеи заканчиваются.

Переход на 1-нм техпроцесс также может потребовать новой структуры транзистора. В то же время необходимо помнить, что инженеры часто находят возможность растянуть удовольствие ― придумать что-нибудь этакое, чтобы сделать ещё один шаг вперёд на старых костылях.