Предисловие

Очень рад в подробностях рассказать о своей первой интегральной схеме и поделиться перипетиями этого проекта, которым занимался на протяжении прошлого года. Надеюсь, мой успех вдохновит других и поможет начать революцию в производстве домашних микросхем. Когда я приступил к этому проекту, то понятия не имел, во что ввязался, но в итоге узнал больше, чем когда-либо думал, о физике, химии, оптике, электронике и многих других областях.

Кроме того, мои усилия сопровождались лишь самыми положительными отзывами и поддержкой со всего мира. Искренне благодарен всем, кто мне помогал, давал советы и вдохновлял на этот проект. Особенно моим удивительным родителям, которые не только всегда поддерживают и поощряют меня как только могут, но и предоставили рабочее место и смирились с затратами на электроэнергию… Спасибо!

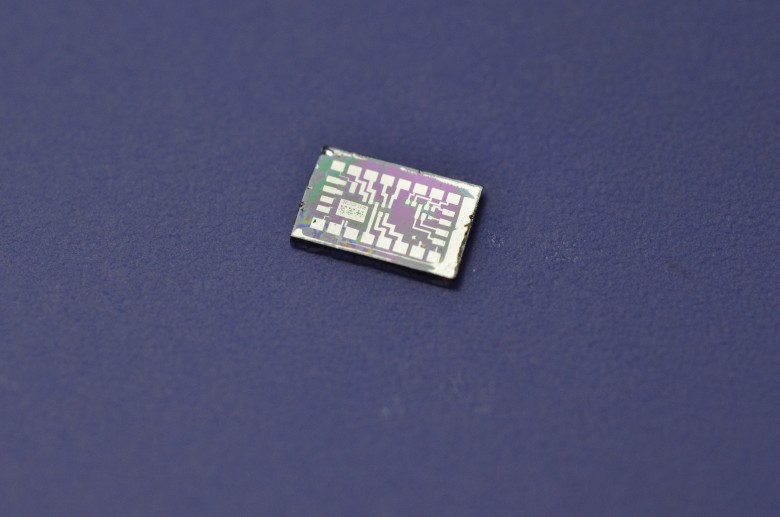

Без дальнейших церемоний представляю первую интегральную схему (ИС), изготовленную литографическим способом в домашних (гаражных) условиях — PMOS-чип двойного дифференциального усилителя Z1.

Я говорю «изготовленную литографическим способом», потому что Джери Эллсуорт изготовил первые транзисторы и логические вентили (с соединениями, тщательно проложенными вручную проводящей эпоксидной смолой) и показал миру, что это возможно. Вдохновленный его работой, я представляю интегральные схемы, созданные масштабируемым, стандартным фотолитографическим процессом. Излишне говорить, что это логический шаг вперёд по сравнению с моим предыдущей работой, где я воспроизвёл полевой транзистор Джери.

Дизайн

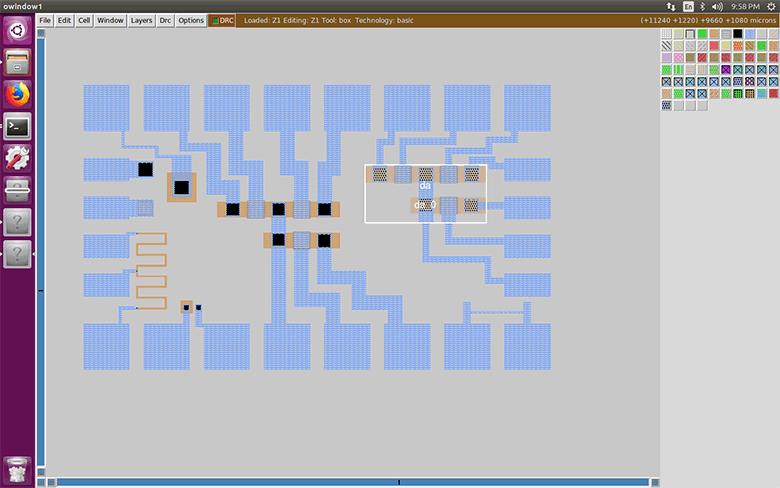

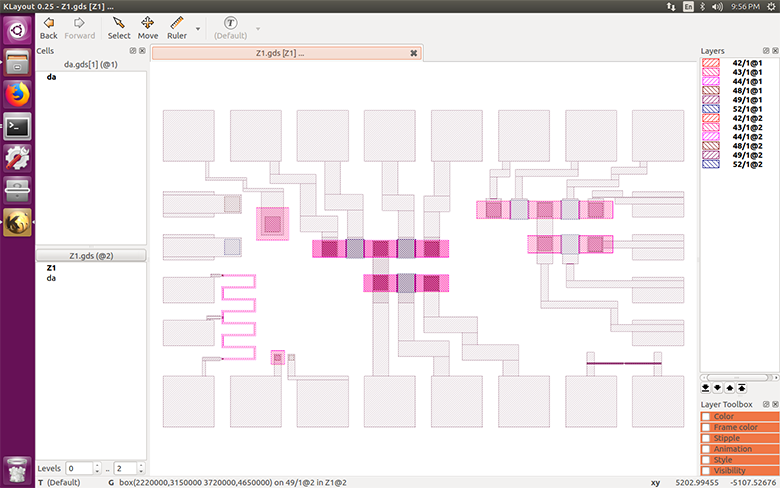

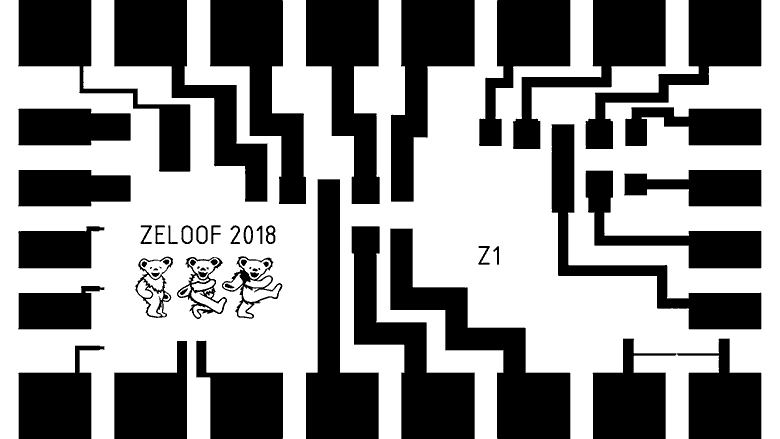

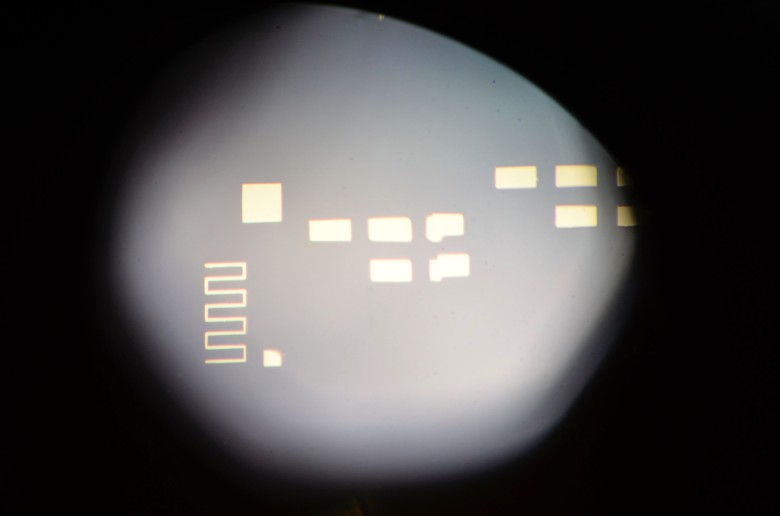

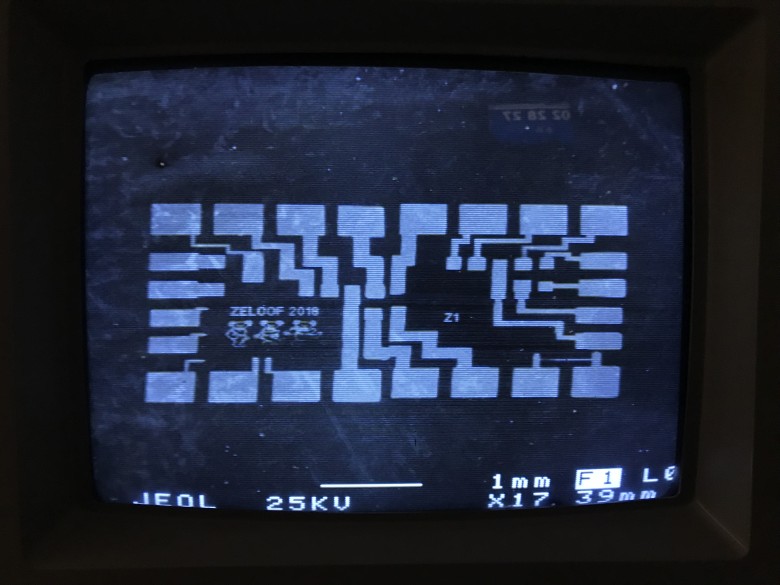

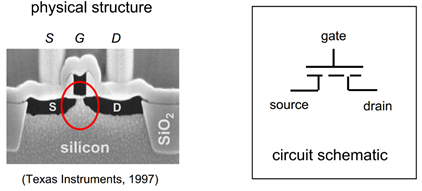

Я разработал усилитель Z1, когда искал простой чип для тестирования и настройки своего процесса. Макет сделан в Magic VLSI для процесса PMOS с четырьмя масками (активная/легированная область, подзатворный оксид, контактное окно и верхний металлический слой). У PMOS есть преимущество перед NMOS, если учесть ионные примеси из-за изготовления в гараже. Маски разработаны с соотношением сторон 16:9 для упрощения проекции.

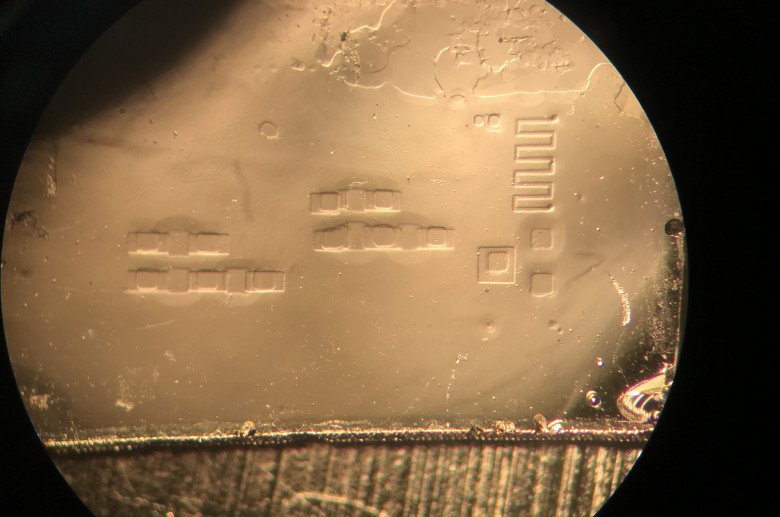

Размер затвора приблизительно 175 мкм, хотя на чипе для проверки выполнены элементы размером до 2 мкм. Каждая секция усилителя (центральная и правая) содержит три транзистора (два для двухтактной схемы с общим катодным сопротивлением и один в качестве источника тока/нагрузочного резистора), что означает в общей сложности шесть транзисторов на ИС. В левой части резисторы, конденсаторы, диоды и другие тестовые элементы, чтобы изучить характеристики техпроцесса. Каждый узел дифференциальных пар выходит отдельным штифтом на выводной рамке, поэтому его можно изучать, а при необходимости добавить внешнее смещение.

Изготовление

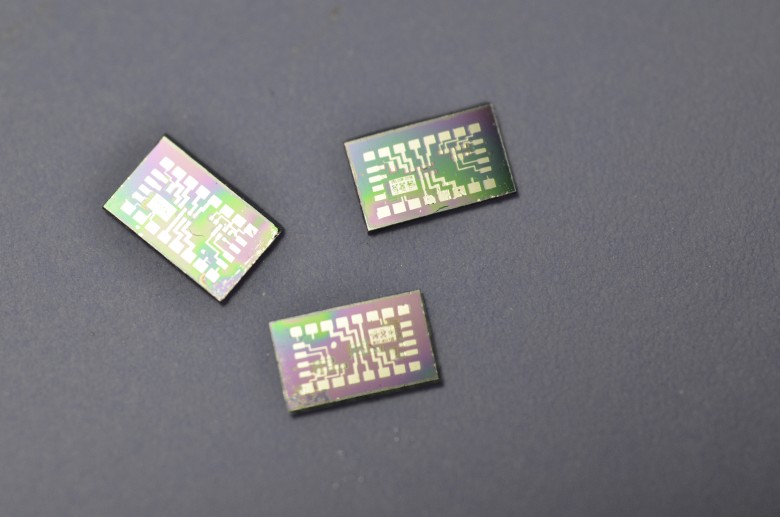

Процесс изготовления состоит из 66 отдельных шагов и занимает примерно 12 часов. Выход достигает 80% для больших элементов, но сильно зависит от количества выпитого кофе в конкретный день. Я также записал видео на YouTube о теории производства микросхем и отдельно об изготовлении МОП-транзисторов.

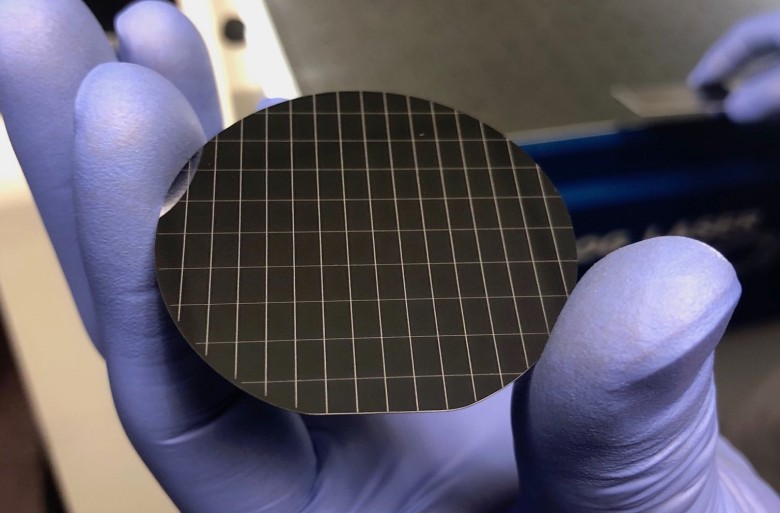

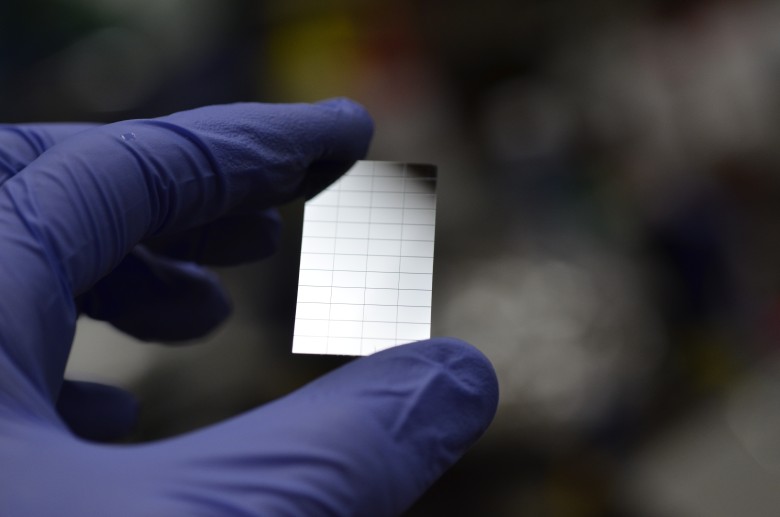

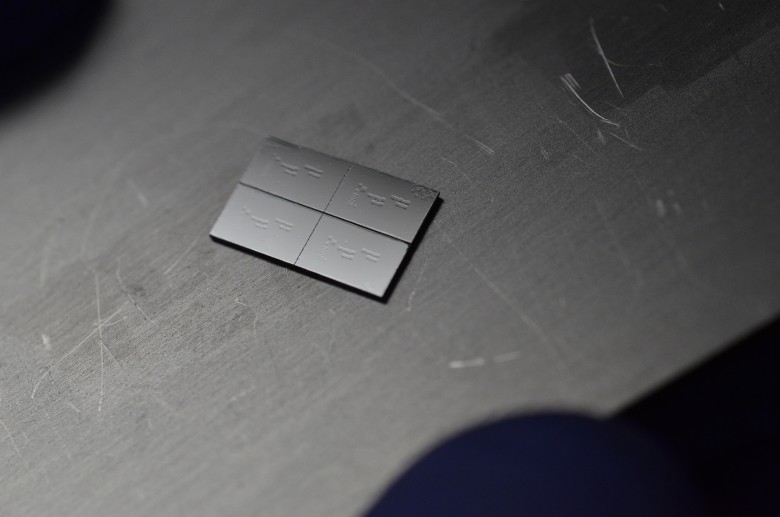

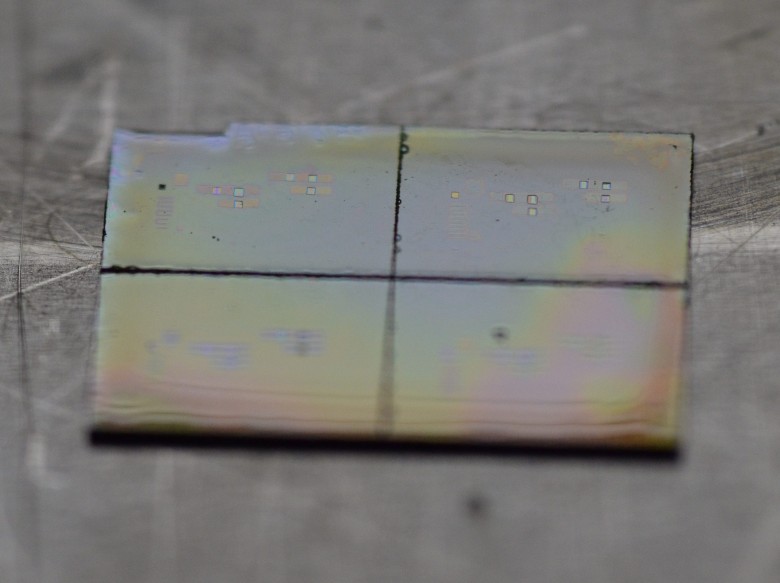

Кремниевые пластины 50 мм (2″) разбиваются на кристаллы 5,08×3,175 мм (площадь около 16 мм²) волоконным лазером Epilog. Такой размер кристалла выбран, чтобы он помещался в 24-контактный DIP-корпус Kyocera.

Сначала с пластины снимается нативная окись быстрым погружением в разбавленный фтороводород с последующей интенсивной обработкой травильной смесью «пиранья» (смесь серной кислоты и перекиси водорода), смесью RCA 1 (вода, аммиак, перекись водорода), смесью RCA 2 (вода, соляная кислота, перекись водорода) и повторным погружением во фтороводород.

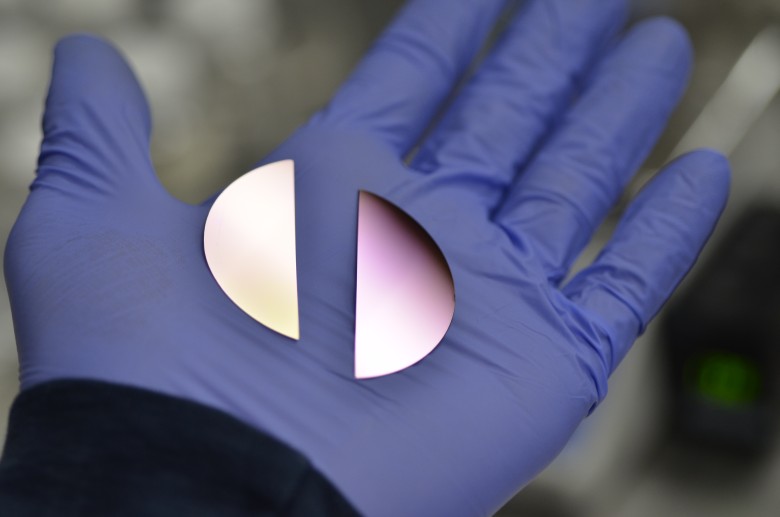

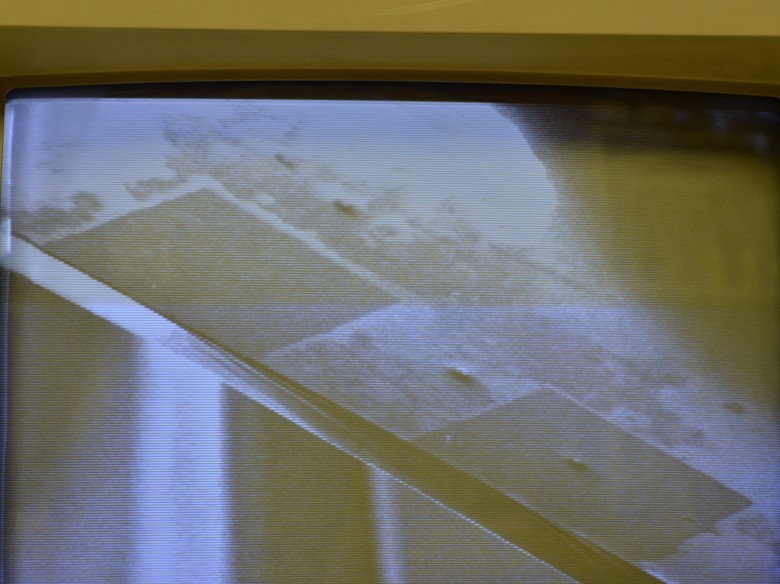

Защитный окисел термически выращивается в водяном паре окружающего воздуха (влажное оксидирование) до толщины 5000−8000 Å.

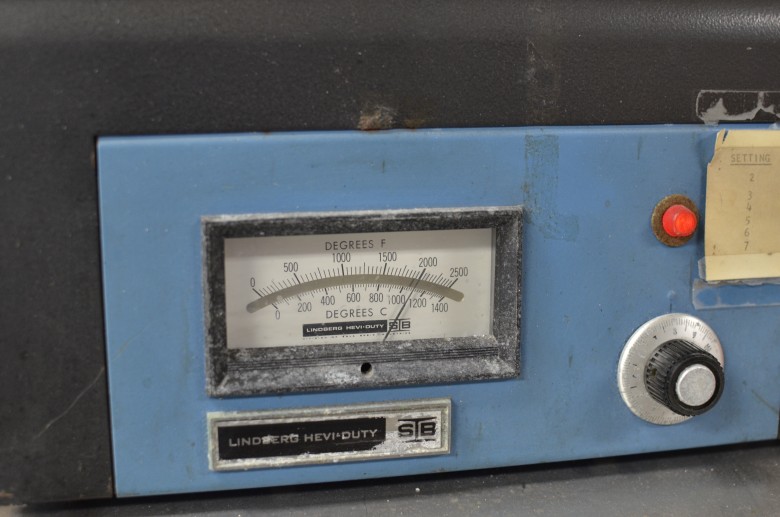

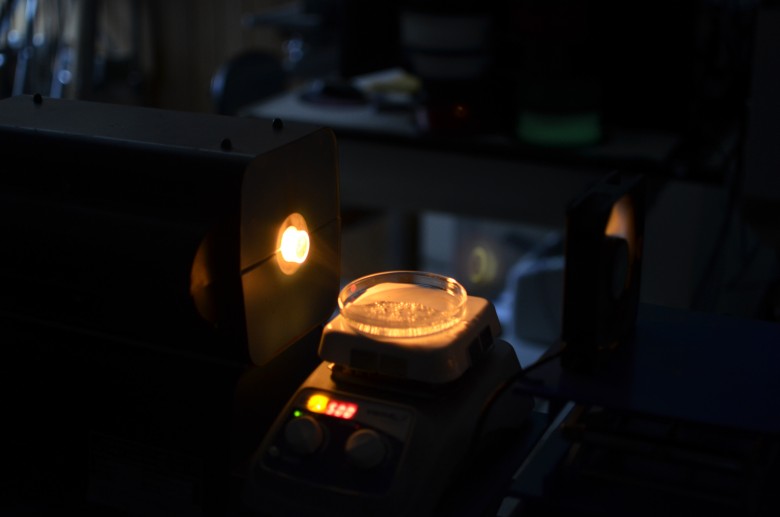

Влажное термическое оксидирование

Влажное термическое оксидирование

Оксидированная пластина готова к формированию рисунка на активной/легированной (Р-типа) области. Фоторезист AZ4210 вращается примерно на 3000 оборотах в минуту, формируя плёнку толщиной около 3,5 мкм, которая аккуратно подсушивается при 90°С на электроплитке.

Маску активной зоны обрабатывает мой фотолитографический степпер Mark IV в ультрафиолете с шагом 365 нм — и структура отрабатывается в растворе гидроксида калия.

После этого структура резиста плотно затвердела и применяется несколько других трюков, чтобы обеспечить хорошее сцепление и химическую стойкость во время следующего вытравливания во фтороводороде, который переносит эту структуру на слой подзатворного оксида и открывает окна к голому кремнию для легирования. Эти регионы позже станут истоком и стоком транзистора.

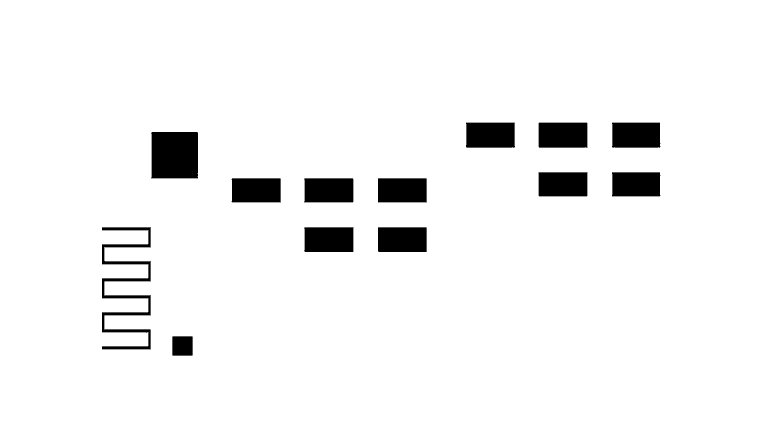

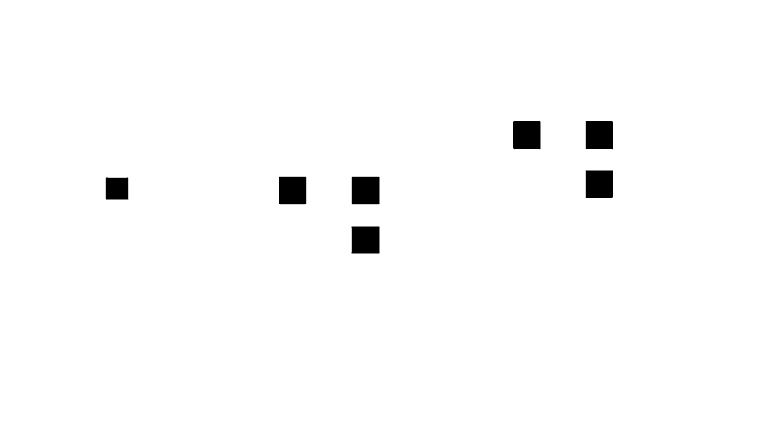

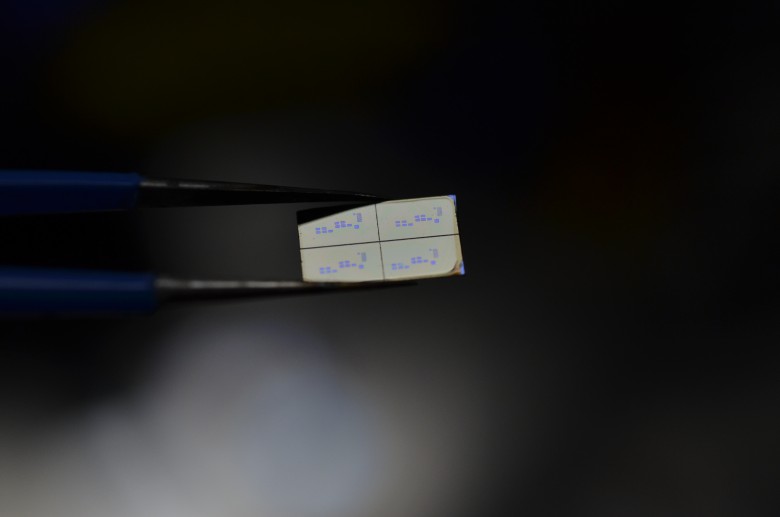

Легированные кристаллы с вытравленными затворами

После этого производится легирование, то есть введение примесей из твёрдого или жидкого источника. В качестве твёрдого источника применяется диск нитрида бора, размещённый поблизости (менее 2 мм) от пластины в трубчатой печи. Как вариант, можно приготовить жидкостный источник из фосфорной или борной кислоты в воде или растворителе — и провести легирование по стандартному процессу преднанесения/погружения во фтороводород/диффундирования/удаления глазури.

Вышеупомянутые шаги формирования рисунка затем повторяются дважды для подзатворного оксида и контактного слоя. Подзатворный оксид должен быть гораздо тоньше (менее ~750 Å), чем защитный оксид, поэтому зоны между стоком/истоком вытравливаются — и там выращивается более тонкий оксид. Затем, поскольку вся пластина оксидировалась на шаге легирования, нужно вытравить контактные окна, чтобы установить контакт металлического слоя с легированными зонами истока/стока.

Теперь все транзисторы сформированы и готовы к межсоединениям с выходом на выводную рамку. Защитный слой алюминия (400−500 нм) распыляется или термически выпаривается на пластину. Альтернативой был бы метод взрывной литографии (lift-off process), когда сначала формируется фоторезист, а затем осаждается металл.

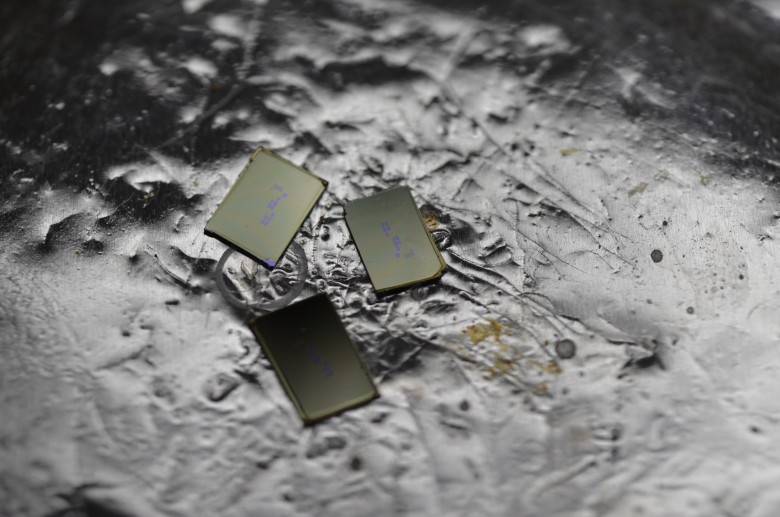

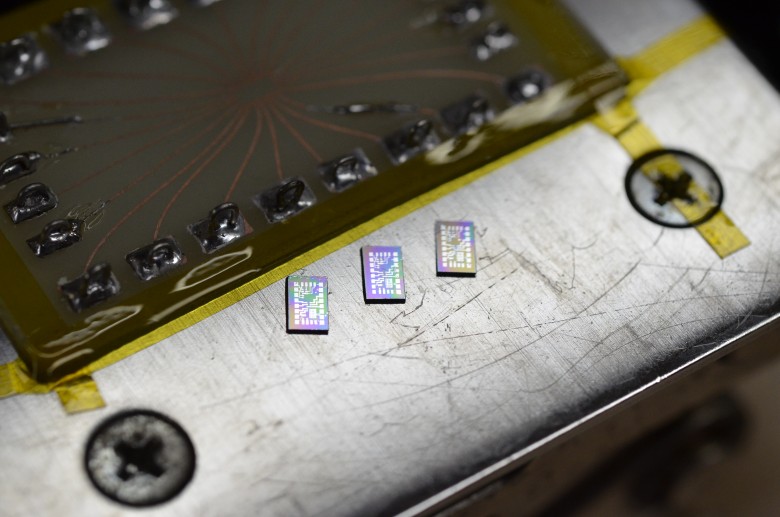

Затем на слое металла формируется рисунок методом фотолитографии и происходит травление в горячей фосфорной кислоте, чтобы завершить изготовление интегральной схемы. Заключительные шаги перед тестированием — это визуальный осмотр и высокотемпературный отжиг алюминия для формирования омических переходов.

Микросхема теперь готова для упаковки и тестирования.

У меня нет установки микросварки (принимаю пожертвования!), поэтому сейчас процесс тестирования ограничен прощупыванием пластины острым пинцетом или использованием платы flip-chip (трудно выровнять) c подключением к характериографу. Дифференциальный усилитель также эмпирически тестируется в цепи для проверки работоспособности.

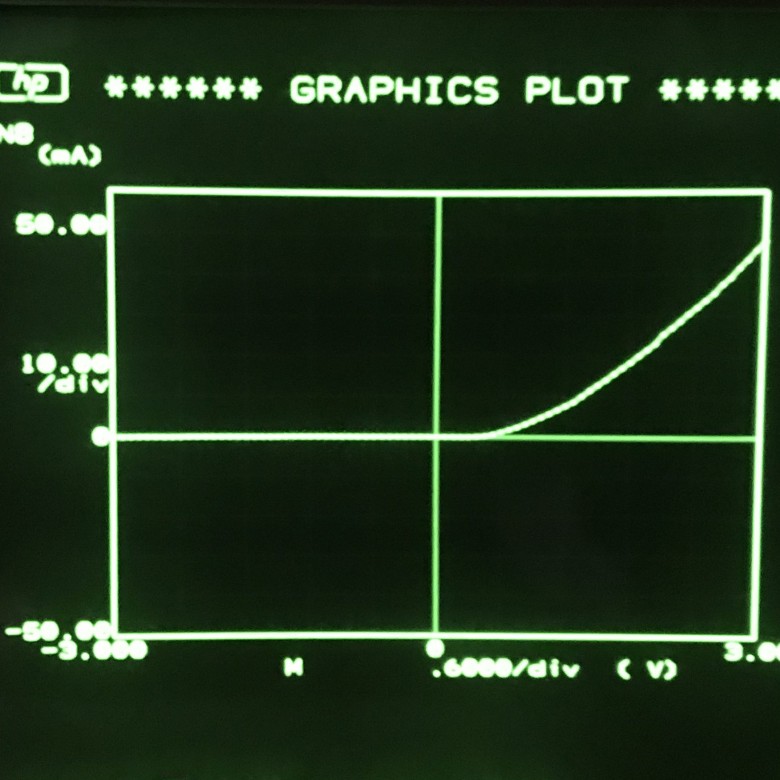

Кривая FET Ids/Vds от с предыдущего устройства NMOS

Конечно, эти кривые далеки от идеальных (в том числе из-за излишнего сопротивления контактов и других подобных факторов), но я ожидаю улучшения характеристик, если раздобуду установку микросварки. Этим могут частично объясняться и некоторые отличия от кристалла к кристаллу. Скоро я добавлю на эту страницу новые кривые IV, характеристики транзистора и дифференциального усилителя.

Источник

![[Перевод] Первая микросхема :) [Перевод] Первая микросхема :)](https://habrastorage.org/webt/za/td/tl/zatdtlesm7s5ehmf7knvou9bklc.jpeg)