Вся история МЦСТ – с 90-х годов по настоящее время – является отличным примером того, как не нужно вести бизнес. Когда во главе компании стоят люди, абсолютно не смыслящие ни в архитектурах, ни в управлении, ни в оптимизации процессов, с абсолютным непониманием меняющейся мировой экосистемы, бросающиеся громкими заявлениями, за которыми ничего не стоит. Эти люди превратили возможно потенциально процветающий бизнес в компанию-паразит, пожирающую государственные средства, в ответ выдавая никому не нужный хлам по видом отечественных микропроцессоров. Процессор Эльбрус. Ахиллесова пята отечественной микроэлектроники. Сколько дифирамб было спето православными адептами этих процессоров… Сколько людей было введено в заблуждение самой политикой МЦСТ, через блоггеров выпуская свои байки об уникальной архитектуре Эльбрус, которой аналогов нет. И всё это не смотря на то, что в сети опубликовано достаточно материалов по разбору тупиковости архитектуры Эльбрус.

Этот материал следующий в списке после цикла статей по разбору строения кристаллов российских микропроцессоров: Байкал М, Эльбрус 8с, Байкал S, Эльбрус 8св, Эльбрус 16с. Сегодня очередь дошла до Эльбрус 8св – последней «высокопроизводительной» микросхемы от компании-паразита.

Разработка этого кремниевого шедевра началась ещё до релиза первой микросхемы Эльбрус 8с, в марте 2014 года по заказу Минпромторга и является существенно переработанной его версией. По итогам почти пятилетней разработки акт приёмки опытно-конструкторских работ был подписан в декабре 2018-го. Изначально 8св именовался как «процессор 9» — шифр осуществленных работ по классификации Минпромторга. Количество произведенных микросхем Эльбрус 8св неизвестно как и в целом линейки процессоров архитектуры Эльбрус. МЦСТ не оглашает подобного рода информацию, однако общее число всех микропроцессоров, разработанных МЦСТ на архитектуре e2k и произведенных на тайваньской фабрике TSMC за всё время, составляет максимум порядка 20-30 тысяч единиц. Последний заказ от прошлого года на 20 тысяч единиц остаётся подвешенным после того как TSMC отказалась производить и поставлять Эльбрусы. Исходя из текущей ситуации, можно предположить, что в сейчас МЦСТ располагает партиями из нескольких сотен Эльбрус 8св и Эльбрус 2с3, произведенная до 2022 года.

Совсем недавно, в конце мая текущего года, появилась новость о закупке МВД 23 серверов на базе процессоров Эльбрус 8св из старых запасов. Использование этого чипа оправдано, поскольку процессоров предыдущего поколения, Эльбрус 8с, уже не осталось ни у МЦСТ, ни у партнеров компании. Тендер был объявлен 15 мая 2023 года в формате электронного аукциона с начальной максимальной ценой контракта в 86,2 млн руб. Заявки от претендентов принимались до 24 мая, а итоги подведены 25 мая. Как не трудно посчитать, победитель снизил стартовую цену лота примерно на 870 тыс. руб. Скорее всего заявка второго участника содержала более выгодное для заказчика предложение. Однако она была признана несоответствующей условиям закупки. МВД ожидает поставку серверов не позднее 30 сентября 2023 года.

Помимо прочего, поголовный отказ в финансировании МЦСТ и явный недостаток произведенных процессоров с низкой производительностью в реальных задачах ставит крест на репутации за МЦСТ, за которой итак стоят много неудобных моментов, о которых они умалчивают.

Речь идёт о нарушении GPL – открытого лицензионного соглашения, НО с определенными нюансами. Чтобы приобрести систему на Эльбрусе, вам необходимо подписать NDA (соглашение о неразглашении). Для приобретения операционных систем Альт или Астру под Эльбрус вас спросят, подписывали ли вы NDA с МЦСТ и если нет, вам поступит отказ. Астра и Альт скажут, что доступ к исходникам они дать не могут и это собственность МЦСТ, а последняя сообщит, что он распространяется только ограниченному кругу лиц. Таким образом, МЦСТ заставляет производителей программного обеспечения нарушать GPL при помощи NDA и доступа к платформе. Привлечь к ответственности руководство МЦСТ за такие махинации уже становится событием с маловероятным исходом.

В декабре 2021-го года Максим Горшенин предоставил нам микропроцессоры Эльбрус 8св на вскрытие. Давайте разберем строение кристалла этой микросхемы и посмотрим чем он отличается от своего старшего брата Эльбрус 8с в плане компоновки элементов на чипе.

Эльбрус 8св является специализированным процессором для обработки информации в составе вычислительных средств с производительностью терафлопсного диапазона. Процессор выполнен в том же форм-факторе BGA что и старший брат 8с с аналогичным числом выводов и размером подложки.

Сам кристалл микросхемы стал чуть больше предшественника на 11 квадратных миллиметров – 341,5 против 330,4.

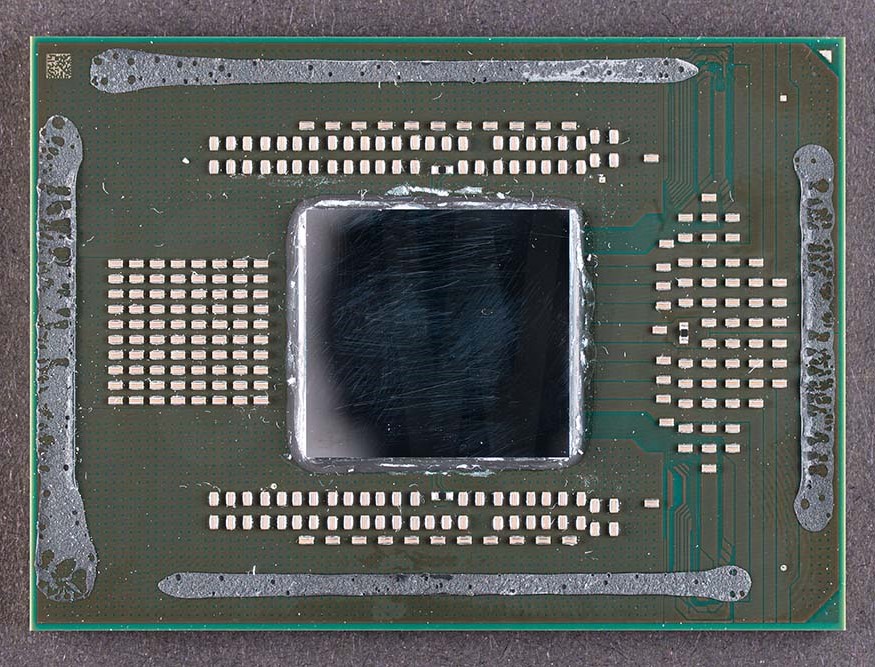

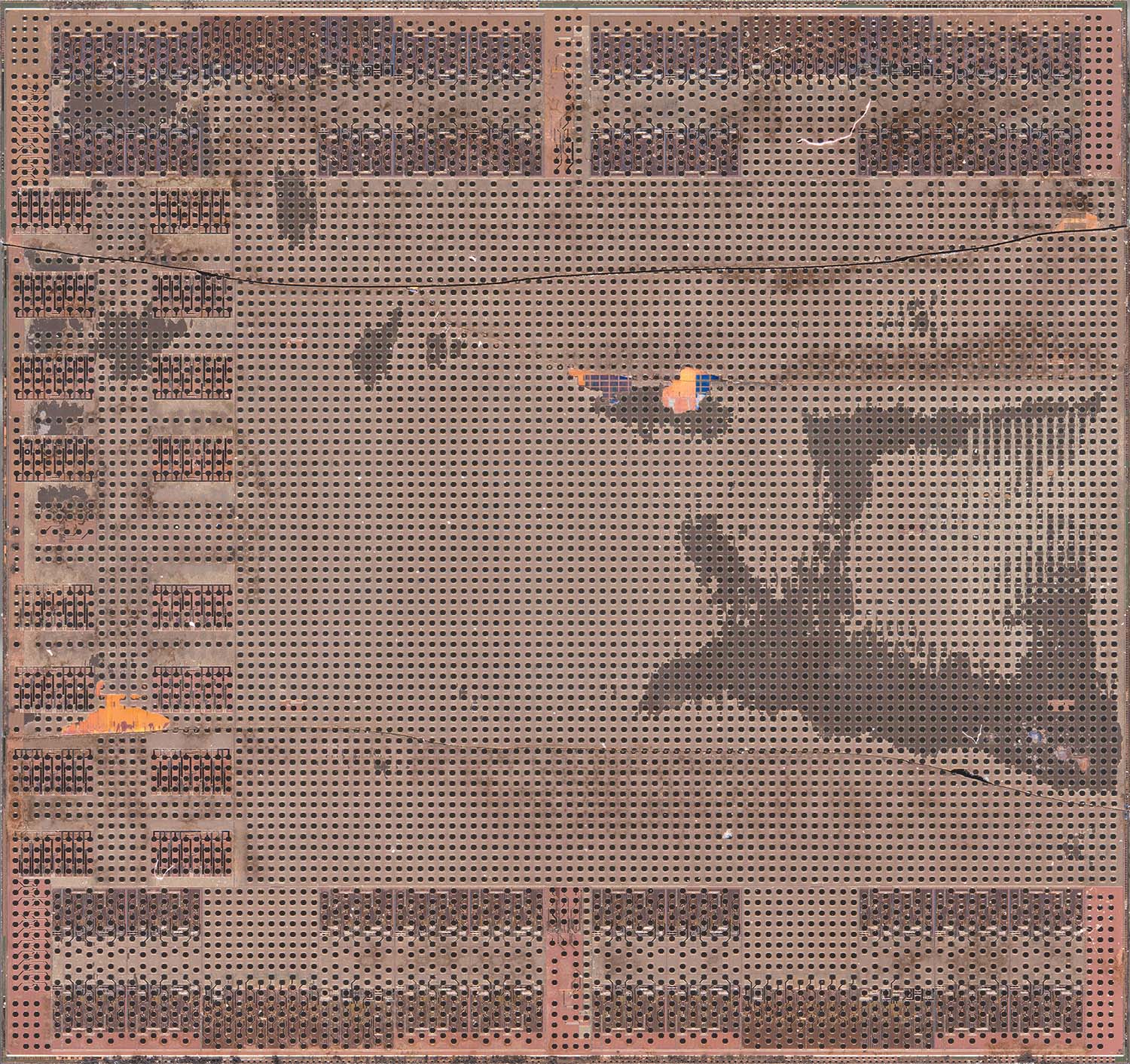

После отделения чипа от подложки видим верхний металлический слой. По расположению контактов, можно определить, что компоновка микросхемы претерпела небольшие изменения в сравнении с Эльбрус 8с.

Сторона полупроводниковых структур и слоев металла кристалла имеет объемные выводы по всей площади поверхности. Сигнальные выводы размещены по периферии поверхности кристалла, а выводы земли и питания занимают центральную часть поверхности. В описании к видео прикреплена ссылка на изображение с описанием каждого из 2028 выводов на подложке чипа, по которым можно приблизительно определить расположение функциональных блоков. В правом верхнем углу обозначен старый логотип МЦСТ, модель и год изготовления микросхемы.

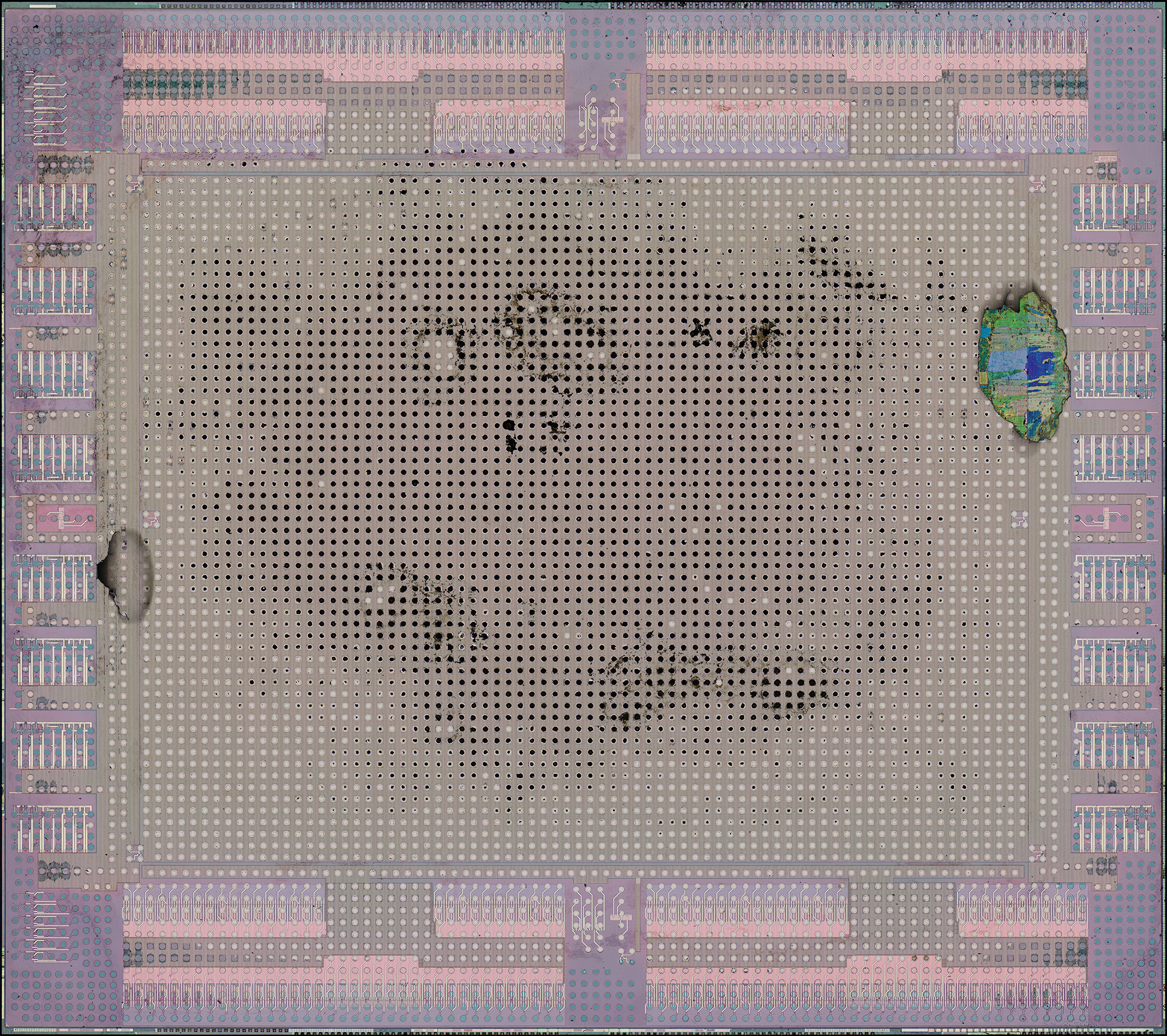

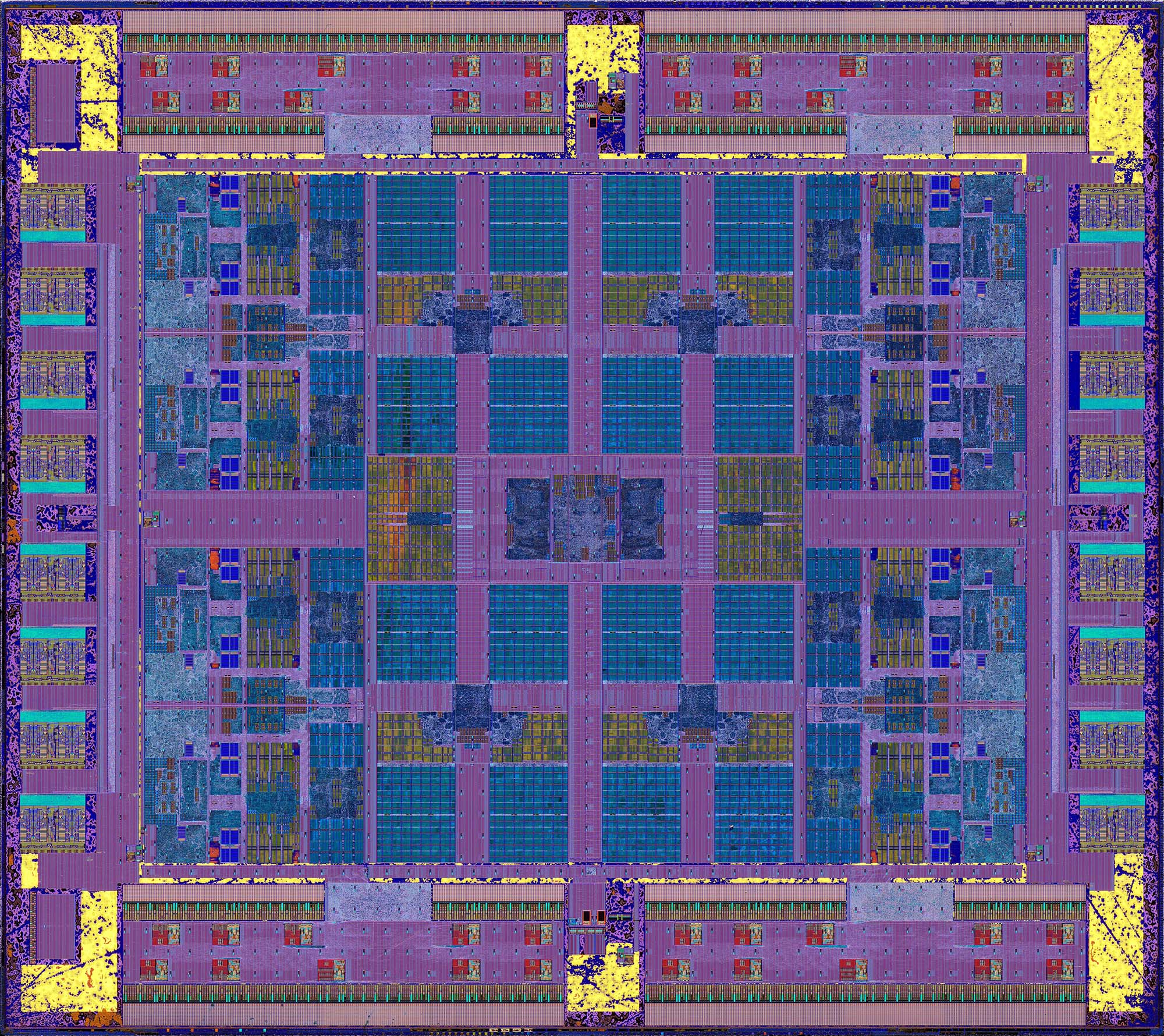

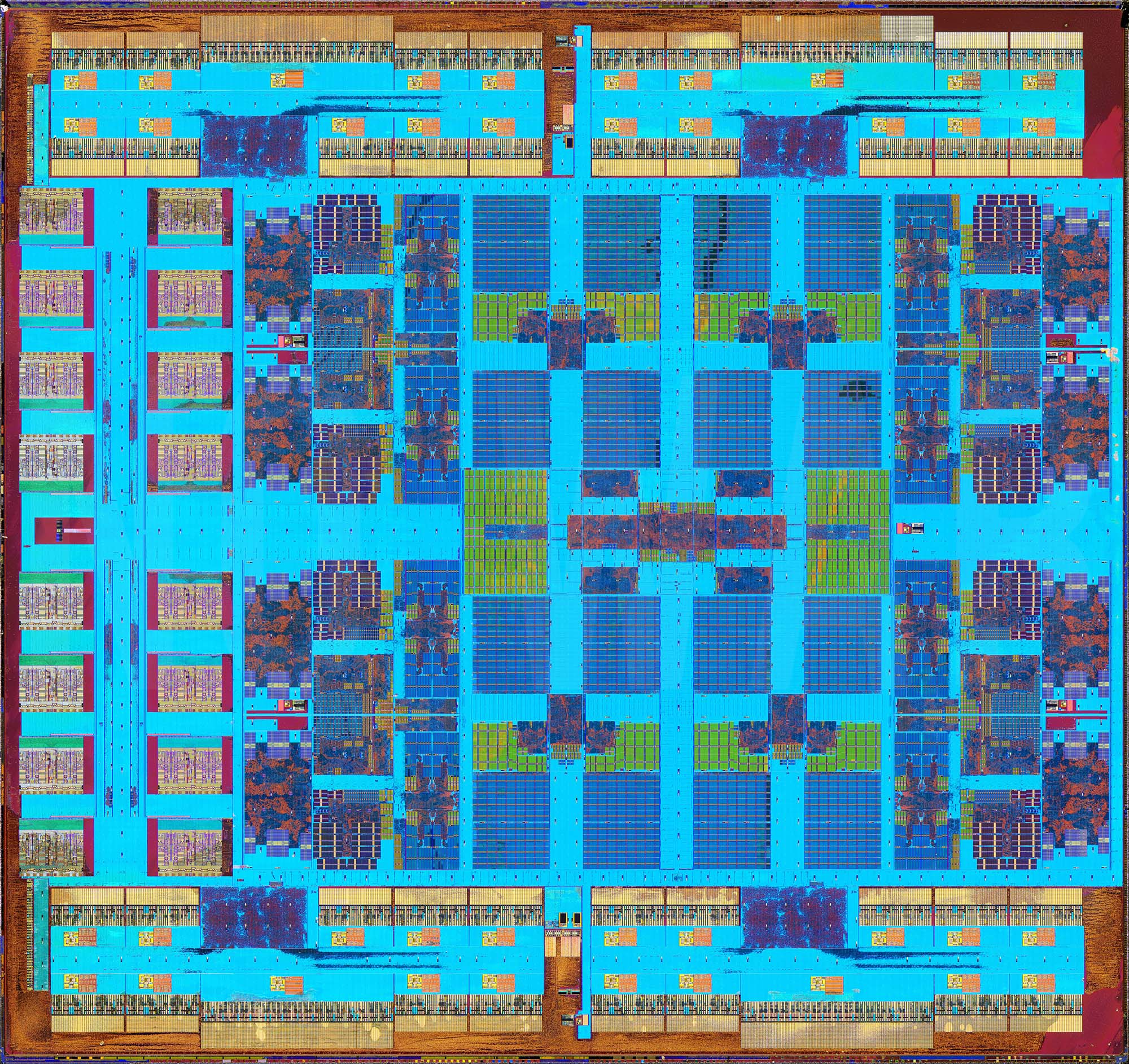

Стравим металлический слой до поликремния, обнажая всю внутреннюю структуру микросхемы.

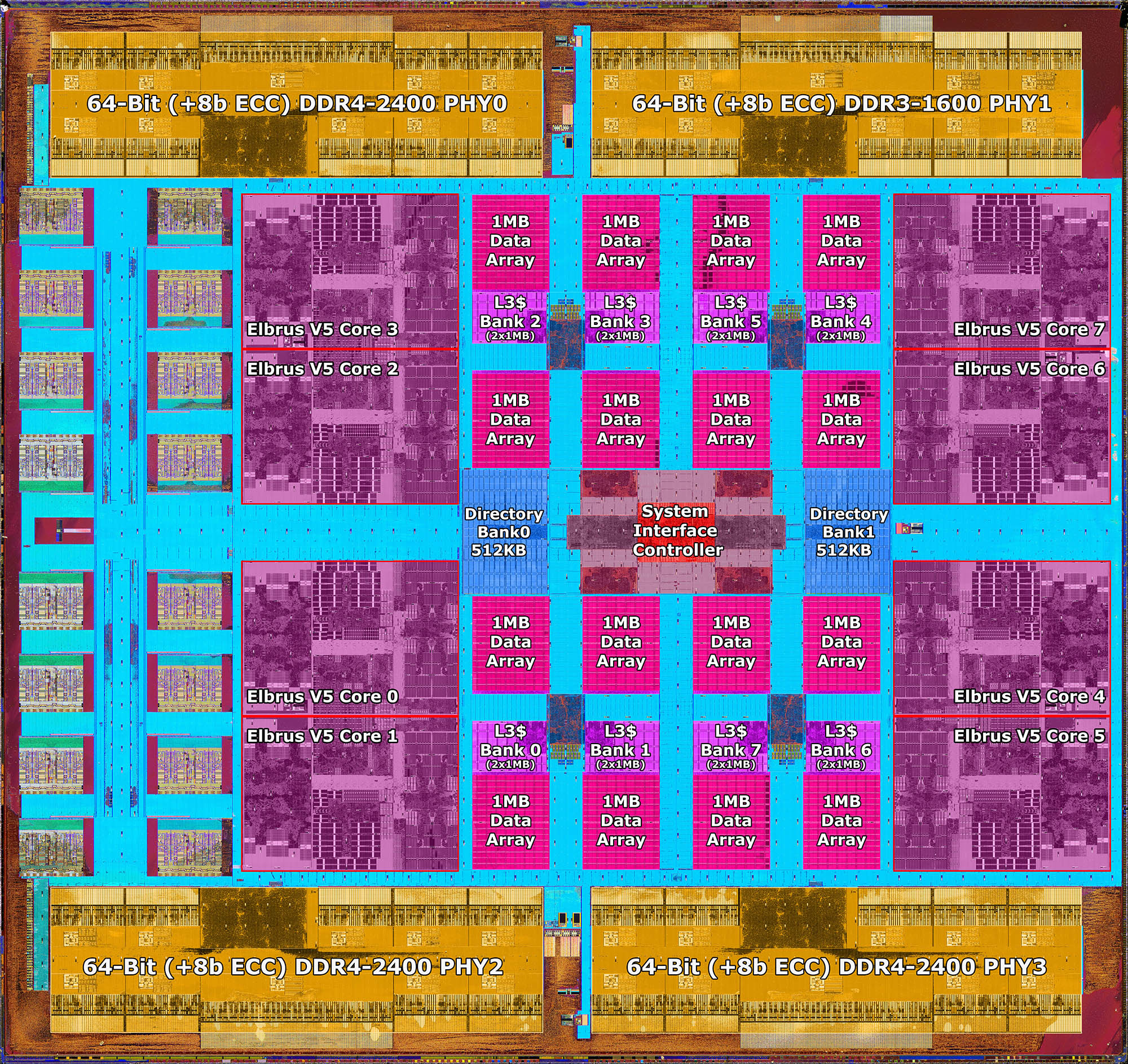

Компоновка элементов на кристалле изменилась незначительно. В состав процессора также входят 8 процессорных ядер на микроархитектуре Эльбрус 5-го поколения с тактовой частотой до 1,5 ГГц. Общий кэш третьего уровня объёмом 16 Мбайт, отвечающий за поддержку межъядерной когерентности и разрешающий все конфликтные ситуации между запросами от ядер своего процессора и когерентными запросами от других процессоров. Контроллер системного обмена SIC, обеспечивающий доступ к оперативной памяти и подсистеме ввода/вывода, подключенным к микропроцессору, и взаимодействие с другими микропроцессорами многопроцессорной системы через межпроцессорные каналы. Системный коммутатор SC в контроллере SIC, обеспечивающий обработку запросов к «своей» оперативной памяти от различных абонентов (L3-кэш, другие микропроцессоры, пространство ввода-вывода) и доступ к системным ресурсам. Для уменьшения когерентного трафика в многопроцессорной конфигурации используется глобальная директория, которая отслеживает состояние строк «своей» памяти находящиеся в других процессорах. Сверху и снизу аналогично компоновке Эльбрус 8с располагаются четыре контроллера оперативной памяти следующего поколения DDR4-2400. Они организуют доступ к четырём секциями локальной оперативной памяти микропроцессора размером до 64 Гбайт каждая. Максимальный суммарный доступный объем локальной памяти составляет 256 Гбайт. Каждый контроллер МС реализует полудуплексный канал DDR4 шириной 8 байт с частотой обмена до 2,4 ГГц. Таким образом, один канал обмена с памятью обеспечивает максимальную пропускную способность 19,2 Гбайт/с с максимальным темпом обмена данными с памятью по трем каналам 76,8 Гбайт/с.

Ядра Эльбрус 8св существенно отличаются от предшественника — у 8с ядро физически было разделено на 2 кластера «А» и «Б». В каждом кластере по 3 АЛУ/ФПУ и своя копия регистрового файла (RF) и кэша L1. Данные RF и кэша L1 совпадали в обоих кластерах.

У 8св теперь монолитное ядро на 6 АЛУ/ФПУ и всего один RF и кэш L1. Для кэша L1 была разработана новая ячейка памяти, что в принципе позволяет этому кэшу работать на частотах вплоть до 2,5 ГГц. Для повышения производительности в 8св в 2 раза были увеличены векторные блоки для работы с целыми и плавающей запятой с 64 до 128 бит. Так же до 128 бит были увеличены регистры в RF. В состав каждого ядра входит контроллер обращения к памяти (Memory Access Unit) и кэш второго уровня (L2) аналогичный Эльбрус 8с, составляющий те же 512 Кб на ядро.

В Эльбрус 8св блок ядер и кэша был сдвинут из-за решения по переносу одного из трёх контроллеров межпроцессорных каналов и host-контроллера к левому краю. Если посмотреть на расположение цепей питания на плате и сопоставить со структурной компоновкой чипа, то окажется, что ядра приближены к питанию для удобной подачи энергии, минуя мешающие контроллеры.

Образующие кластер на краю чипа, три контроллера межпроцессорных каналов IPCC обеспечивают доступ в другие микропроцессоры Эльбрус-8СВ многопроцессорной системы. С их помощью может быть выполнено обращение в локальные памяти других микропроцессоров Эльбрус-8СВ и к другим абонентам через их внутренние системные коммутаторы. Общий доступный объем памяти 4-процессорной системы до 1024 Гбайт. Каждый контроллер IPCC реализует канал полнодуплексного обмена шириной 2 байт и пропускной способностью 16 Гбайт/с (по 8 Гбайт/с на прием и на выдачу данных соответственно). Максимальный суммарный темп обмена данными по всем трем каналам – 48 Гбайт/с. Реализации каналов основана на физическом уровне PCI Express. По каналам межпроцессорного обмена передаются, в числе других, и операции поддержки когерентного состояния общей распределенной памяти.

Контроллер канала ввода-вывода IOCC обеспечивает обмен с подсистемой ввода-вывода. IOCC реализует канал полнодуплексного обмена шириной 2 байт и пропускной способностью 16 Гбайт/с (по 8 Гбайт/с на прием и на выдачу данных соответственно). Реализация канала также основана на физическом уровне PCI Express.

По всей площади чипа расположено несколько термодатчиков, показания которых позволяют отслеживать текущую температуру кристалла. Автомат-регулятор сравнивает эти данные с программно задаваемыми пороговыми значениями температуры и соответствующим образом модифицирует управление системной фазовой автоподстройки частоты; целевой функцией является нахождение максимальной частоты, при которой температура не превышает заданного порога.

В последние годы шумиха вокруг Эльбрусов возросла до такой степени, что теперь почти каждый, кто отдаленно знаком с компьютерной техникой в России, может назвать его и обозначить как отечественную разработку. Вместе с тем, появилась некая тенденция у СМИ и блоггеров выставлять Эльбрус и МЦСТ как нечто героическое, что, несмотря на санкции, работа в этом направлении продолжается без поддержки государства и чисто на коммерческой основе.

На самом деле разработки МЦСТ почти на 100% состоят из государственных субсидий и ОКР. Спрос на микропроцессоры инициирован искусственно со стороны государства с помощью законодательных инициатив. На официальном сайте госзакупок можно найти все субсидии, выделенные на разработку Эльбруса. В частности, на проектирование Эльбрус 8св было выделено более 620 миллионов рублей, на Эльбрус 8с – 836 миллионов, на 16с – 2,5 миллиарда.

Основная проблема с МЦСТ сейчас – закрытость. Чтобы начать дела со всем миром, нужно быть открытыми и охотно идти на различного рода сотрудничества с одним НО:

— Права на процессор частично являются гос собственностью, их не дадут сделать открытыми;

— Компилятор полностью закрыт и недоступен публично – что уменьшает число желающих присоединиться к разработке софта и сильно бьёт по экосистеме;

— Малое число доступных процессоров и систем, исчисляемые тысячами. С такими тиражами на рынок не выйти, к тому же нет спонсируемых вендором систем;

— Проблемы с производством на TSMC. Процессоры сейчас нигде не производятся и фактически МЦСТ мертва без возможности быть клиентом контрактного производства.

В отличии от того же x86/ARM/RISC-V, которые нужны всему миру, Эльбрус это РФ-онли архитектура, которая за пределами страны практически никому не нужна.

Бабаян ещё в начале 90-х громко заявлял об уникальной архитектуре Эльбрус-2000. То есть у МЦСТ было достаточно времени, чтобы осознать тупиковость VLIW и начать активно разрабатывать открытую архитектуру или вписаться в уже существующую экосистему. Но этого делать не стали. Предпочли тихо сидеть у кормушки.

Intel Itanium даже с более хорошими показателями, чем Эльбрус – уже умер. Следовательно Эльбрус имеет абсолютно такую же судьбу, как только её снимут с аппарата поддержания жизнедеятельности. Не нужно выдавать нищету за благодетель.