С высотными ядерными взрывами, к счастью, довольно быстро завязали, но и без них работы достаточно, и требования по надежности и долговечности, предъявляемые к современным спутникам, становятся все амбициознее. Рассказать обо всем невозможно, но я постараюсь кратко осветить прошлое и настоящее космических микропроцессоров из разных стран. Почему именно микропроцессоров? Про них больше всего информации и они лучше понятны неспециалистам. Статья получилась длинной, поэтому я разбил ее на две части: ранняя история на примере США и Европы (прямо сейчас) и современная – на примере России (послезавтра). Поехали!

Правила игры

Начнем с терминов и определений. Под «микропроцессором» я понимаю микросхему или комплект микросхем высокой степени интеграции, предназначенный для выполнения программ. Первым популярным однокристальным микропроцессором стал четырехбитный Intel 4004, вышедший в 1971 году – это уже после высадки американцев на Луну, так что при таком определении из рассмотрения выпадают бортовые компьютеры эпохи героического освоения космоса, оставляя нам только скучных “рабочих лошадок”. Впрочем, про бортовые компьютеры героической эры и так много написано, в том числе и на Хабре. Вот, вот и вот. Они, как правило, проектировались под конкретную миссию, имели какую-придется систему команд и разрядность то 13 бит, то 17, то 21 – в общем, не пытайтесь повторить в домашних условиях. Унификация началась с урезанием бюджетов после окончания лунной гонки и с одновременным развертыванием разнообразных спутниковых группировок. В итоге практически все заинтересованные стороны пришли к ограниченному числу универсальных чипов, используемых везде, где получается.

Второй важный момент – доступность информации. Космическая отрасль никогда не была особенно открытой. Первый спутник, выход астронавтов на Луну или количество спутников в группировке ГЛОНАСС – это простая и понятная реклама, а вот особенностями конструкции радиопередатчика в «Спутнике-3» хвастаться на потребительском уровне затруднительно. Добавим сверху традиционную околовоенную секретность – и вот про процессор RAD750 мы знаем, что «их летает больше 150», и только десяток спутников, на которых он стоит. Типовая цитата из профильных научных публикаций, написанных в семидесятых, выглядит вот так: “A radiation-hard 32-bit PMOS/SOS shift register has also been built and tested; however, test data on this circuit are classified.” Про открытые данные о российских спутниках и микросхемах (а я, разумеется, пользуюсь только открытыми данными) не хочется даже начинать; имеющиеся крохи обычно попадают в интернет по недосмотру. Ситуацию немного спасают научные публикации – особенно если знать, что именно вы ищете. Онлайн-база IEEE – просто кладезь для историка электроники; с архивами советских и российских научных журналов и конференций ситуация радикально хуже, чем с зарубежными, но тоже не безнадежная. Минус публикаций в том, что через них сложно проследить связь между микросхемами и их применением, но интересную информацию о конструкции микросхем найти вполне можно. Итого: статья не претендует на полноту, она – скорее сборник примеров, по которым можно проследить развитие и представить нынешнее состояние микропроцессоров и микроконтроллеров космического применения.

Третье, о чем надо договориться – я не буду сравнивать производительность процессора марсохода с айфоном. В этом есть некоторое веселье, но разница в производительности – не от хорошей жизни, у нее есть объективные причины: длительный цикл разработки, другие требования по надёжности, продолжительная сертификация и тестирование всего, от технологии производства микросхем до спутника в сборе. Разумеется, космические разработчики всегда хотят получить максимум вычислительной мощности – чтобы обрабатывать информацию на борту, экономя пропускную способность радиоканала – но часто другие приоритеты оказываются важнее. Именно поэтому от завершения разработки до первого полета может пройти лет десять, и поэтому же все любят уже летавшие решения – с ними гораздо меньше мороки. В итоге срок жизни космических микросхем может составлять тридцать-сорок лет, разработка нового поколения может начаться ещё до первого полета предыдущего, а прямо сейчас еще запускаются в процессоры, разработанные в девяностых. Тут же замечу, что конструкция космических аппаратов все усложняется и усложняется, и сейчас на борту могут быть десятки вычислителей, к которым предъявляются очень разные требования: нужны и обработка массивов изображений в круглосуточном режиме, и опрос пары датчиков раз в час.

Четвертое – очень краткая напоминалка о радиационных эффектах космического пространства. Напоминалка средней длины есть тут, а совсем длинная – вот здесь.

Эффекты полной дозы излучения связаны с накоплением электрического заряда в диэлектриках и на границе раздела диэлектрика и полупроводника; в основном нас интересуют подзатворный оксид и боковая изоляция МОП-транзисторов. Проявляются эти эффекты как сдвиг порогового напряжения транзисторов (у p-канальных рост по модулю, у n-канальных обычно уменьшение, но дальше вы увидите нюансы), падение подвижности носителей заряда (уменьшение скорости работы схемы) и появление утечек в n-канальных транзисторах (как между стоком и истоком одного транзистора, так и между разными транзисторами), приводящих к росту статического энергопотребления.

Одиночные эффекты обусловлены тем, что при попадании в транзистор одиночной заряженной частицы часть энергии этой частицы передается материалу микросхемы, и в нем образуются свободные электронно-дырочные пары. Часть этих пар разделяется в микросхеме электрическим полем, и она “видит” короткий импульс тока, “принесенный” внешней частицей. Дальше этот импульс тока может изменить значение, записанное в ячейке памяти, попасть на вход логического элемента или вовсе сделать что-то катастрофическое, например, пробить затвор транзистора или открыть паразитную тиристорную структуру и создать локальную закоротку земли с питанием.

Эффекты смещения связаны с тем, что прилетевшая частица может не только создавать электронно-дырочные пары, но и взаимодействовать непосредственно с атомами вещества, выбивая их с нужных позиций в кристаллической решетке. Для обычных транзисторов такие локальные дефекты не страшны, но они приводят к значимым повреждениям оптоэлектронных приборов, двухмерных полупроводников и наноразмерных транзисторов.

Еще существуют эффекты мощности дозы, но они имеют в основном некоммерческие приложения, поэтому я о них говорить не буду.

Начальный этап – на примере США

То, что мне не удалось достоверно выяснить, какой микропроцессор стал первым на борту космического аппарата, было довольно предсказуемо. Публичные данные есть только на широко известные научные миссии, а на них обычно ставят самое надежное и проверенное, то есть тихо отработанное заранее на менее дорогих спутниках. Известно, что бортовые вычислители Viking и Voyager были собраны еще на дискретной логике, зато именно на них начались стандартизация и переиспользование компонентов. Voyager интересен тем, что он стал первым аппаратом м, на котором была использована полупроводниковая память вместо магнитных сердечников. Причем это была энергозависимая CMOS SRAM, то есть информация в ней стирается в случае, если пропадает питание. Как инженерам удалось убедить руководство пойти на такой риск? Во-первых, без новой памяти не было бы смысла применять быструю КМОП-логику. В космосе КМОП-технология была более чем кстати: несмотря на то, что КМОП-схемы были медленнее биполярных аналогов и намного чувствительнее к электростатическому разряду, они хорошо переносили перепады температур, имели низкую чувствительность к шумам и потребляли радикально меньше мощности, которой на борту обычно был дефицит. Во-вторых, в качестве бэкапа питания к памяти напрямую подвели напряжение с выхода РИТЭГ, разумно рассудив, что если с генератором что-то случится, то проблемы с памятью уже не будут актуальны.

Рисунок 1. Плата с полупроводниковой памятью с Voyager.

Самые первые – RCA 1802

Самый ранний из найденных мной космических аппаратов, в которых стояли не микросхемы средней степени интеграции, а именно монолитный микропроцессор (8-битный RCA 1802) – это спутник Magsat, запущенный 30 октября 1979 года. Учитывая, что первые коммерческие RCA 1802 были выпущены в 1975 году, это должно означать, что в NASA они попали раньше, чем на прилавки магазинов – что, в общем, было нормальной практикой на раннем этапе существования Кремниевой долины.

В качестве небольшого примера из той эпохи процитирую статью E.E. King, “Effects of Total Dose on 1802 Microprocessor”, IEEE Transactions on Nuclear Science, 1977. В статье сравнивается воздействие дозы радиации на четыре варианта 1802: два коммерческих, один экспериментальный образец, произведенный на подложке кремния на сапфире (КНС), и один образец, произведенный по специальному техпроцессу, предназначенному для повышения радиационной стойкости.

Рисунок 2. Сдвиг порогового напряжения транзисторов обоих типов под воздействием дозы излучения. С1 и С2 – коммерческие чипы, S – чип на КНС, X – специальный образец.

Из рисунка видно, что и у коммерческих образцов, и у КНС-чипа на довольно небольших дозах излучения (8-15 крад(Si)) порог n-канальных транзисторов становится меньше нуля, и логические схемы просто перестают переключаться. В то же самое время специальный техпроцесс позволил добиться стойкости больше 1 Мрад(Si), то есть на два порядка больше. Еще раз замечу, что на дворе еще только 1977 год, а специальные чипы уже разработаны и произведены. Впрочем, описанный RCA 1802 скорее всего был первой ласточкой, потому что в воспоминаниях участников разработки следующего большого аппарата NASA – Galileo – я нашел рассказ о том, что на момент выбора архитектуры управляющей электроники в 1977 году 1802 был единственным доступным радстойким монолитным микропроцессором.

Важно отметить, что использовать самые обычные чипы в космосе пытались уже тогда – и продолжают успешно делать это сейчас. Для многих приложений не нужны ни экстремальная надежность, ни большая радиационная стойкость, ни полное отсутствие сбоев – важно только отсутствие отказов в какой-то разумный период времени, а с этим требованием многие коммерческие чипы справляются, будучи при этом на несколько порядков дешевле своих специально разработанных собратьев. Для спутниковой группировки из нескольких сотен аппаратов на низкой орбите даже наличие не очень частых отказов не критично, в отличие от стоимости. И только там, где от функционирования микросхем зависит безопасность страны, жизнь космонавтов или хотя бы судьба многомиллионной десятилетней научной миссии, без радстойких чипов никак. Существуют, разумеется, и смешанные подходы, когда наиболее критичные системы выполняются на радстойких чипах, а остальное – на обычных, а также known good die, когда производитель берет те же самые кристаллы, что используются в дорогих радстойких продуктах, пакует их в дешевые пластиковые корпуса и не проводит сквозное тестирование, экономя на цене в несколько раз. Есть и компании, специально занимающиеся тестированием коммерческих чипов, чтобы найти среди них те, которые случайно получились радстойкими. Но вернёмся к Galileo и 1802.

Рисунок 3. Запуск Galileo c Space Shuttle. Бортовые вычислители самого шаттла, созданные в семидесятых, работали на микросхемах малой степени интеграции, и только в ходе большого апгрейда, сделанного уже в двухтысячных, на борт попали радстойкие 386-e, 1802-е и гражданские PowerPC 750.

Galileo в силу различных проблем полетел только в 1989 году, но дизайнился почти сразу после «Вояджеров» и с использованием их наработок. “1802 никому в команде разработчиков по-настоящему не нравился”, так как дискретные решения, хоть и более громоздкие, были намного быстрее. В итоге в его плюсы все же перевесили минусы, и подсистема команд и данных аппарата (Command and Data Subsystem) была построена на 1802, а менее загруженная, но более требовательная к скорости подсистема управления маневрированием (Attitude and Articulation Control Subsystem) управлялась 16-битным компьютером, собранном из биполярных четырехбитных bit-slice микросхем Am2900 (советский аналог – 1802 серия).

Galileo дополнительно важен для нашей истории тем, что он стал первым аппаратом, в котором была учтена при проектировании проблема одиночных сбоев. В микросхемах, выполненных по грубым проектным нормам, они почти не проявлялись, и об их существовании никто не догадывался, пока исследовательские зонды не достигли радиационных поясов Юпитера. Магнитосфера Юпитера настолько велика, что часть его спутников (Европа, Ио и Ганимед) находится внутри нее! Магнитные поля Юпитера разгоняют до колоссальных энергий тяжёлые ионы, источником которых является вулканически активная Ио. Такие чудовищные условия оказались достаточными для того, чтобы вызвать сбои даже в старых микросхемах «Пионера», а ведь чем меньше проектные нормы, тем меньше энергии нужно, чтобы переключить бит в памяти!

Рисунок 4. Картинка радиации вокруг Юпитера. Источник: Hans Huybrighs, “The feasibility of in-situ observations of Europa’s water vapour plumes”, 2015

К 1977 году, когда началось проектирование Galileo, «Вояджеры» ещё не достигли Юпитера, и все доступные данные по радиации касались только «Пионеров». Часть их загадочных ошибок была позже классифицирована как одиночные сбои, но это было позже, а пока что в бортовую аппаратуру Galileo не было ни заложено ни самокорректирующихся кодов, ни каких-то других способов находить и исправлять ошибки. После того, как вероятная причина сбоев в «Пионерах» и «Вояджерах» была найдена (1982 год), все электронные компоненты «Галилео», подобранные так, чтобы быть устойчивыми к дозе излучения, срочно отправили на ускоритель: выяснять, как они будут справляться с новой проблемой. Результаты оказались неутешительными: если 1806, выполненный по относительно старой технологии, вел себя нормально, то в прогрессивном биполярном микропроцессорном комплекте 2901 от 20 до 50% попаданий заряженных частиц вызывали сбои, и запускать его было нельзя. Что делать? Было найдено два варианта:

- Попробовать новейший радстойкий бортовой компьютер на основе архитектуры 1750А и перекомпилировать весь софт, предварительно написав компилятор. Стоимость этого варианта оценили в 20 миллионов долларов (тогдашних долларов, они были существенно дороже нынешних).

- Экстренно заказать разработку сбоеустойчивых аналогов проблемных чипов 2901. При этом весь многократно проверенный софт можно было не переделывать. Sandia Labs оценили разработку новых микросхем в 5 миллионов, и решение было принято.

NASA Tech Briefs, Volume 10, Issue 3 дает немного подробностей о разработанных Sandia Labs чипах: они были не биполярные, как оригинал, а КМОП, их было девять типов (из примерно сорока чипов исходной серии), и для достижения сбоеустойчивости в них были использованы более широкие, чем нужно, транзисторы, а также резисторы в цепях обратной связи запоминающих элементов.

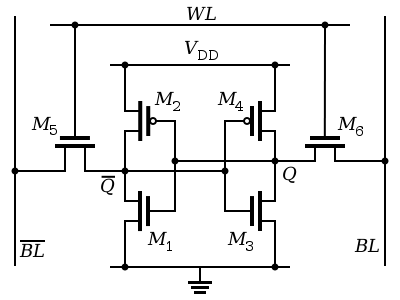

Рисунок 5. Схема шеститранзисторной ячейки статической памяти (6T SRAM)

При попадании ТЗЧ в сток закрытого транзистора возникает импульс ионизационного тока, и в ячейке начинаются два процесса: срабатывание положительной обратной связи и рассасывание индуцированного заряда.

Пусть попадание произошло в закрытый транзистор M2, на стоке которого в результате появился импульс тока. Транзистор М1 в этот момент полностью открыт и имеет маленькое сопротивление, то есть индуцированный ТЗЧ ток через него уходит в землю. Однако емкость узла nQ может быть достаточно маленькой для того, чтобы зарядиться до высокого напряжения, что приведет к переключению второго инвертора (M3-M4), который, в свою очередь, через обратную связь переключит и первый инвертор. Это и есть радиационно-индуцированный сбой (single event upset, SEU). Установка резисторов в цепи обратной связи позволяет замедлить процесс срабатывания обратной связи и дать заряду достаточно времени, чтобы рассосаться.

Проектирование SA3000 – радстойкого 8085

О том, как выглядел процесс разработки радстойких микросхем в то время, можно проследить по научным публикациям. В качестве примера я взял статью W. Kim et. al., «Radiation-Hard Design Principles Utilized in CMOS 8085 Microprocessor Family», вышедшую в 1983 в IEEE Transactions on Nuclear Science. В ней сотрудники Sandia Labs рассказывают о том, как они делали SA3000 – радстойкий вариант Intel 8085 (а также SA3001 и SA3002 как варианты RAM Intel 8155 и ROM Intel 8355). Начали они с того, что получили у Intel всю документацию по разработке, включая электрические схемы и топологию. Я бы тоже от такого не отказался, наверное. С RHBP ситуация в этом случае такая же, как в предыдущем – специальный КМОП-техпроцесс с оптимизированным температурным режимом для бездефектности оксидов, заглубленный n+-слой для защиты от тиристорного эффекта. То, что интересно для нас – это подробное описание подходов к RHBD против полной дозы и одиночных сбоев.

Исходный чип был сделан на NMOS-технологии с использованием динамической логики, крайне уязвимой к утечкам, особенно в случае сильного ухода порогов транзисторов. Радиационная стойкость коммерческих образцов составляла от 700 рад(Si) до 30 крад(Si). Лучшие из них в принципе даже можно было использовать на низкой орбите, но для серьезных проектов нужны были уровни дозовой стойкости по крайней мере на порядок больше. Поэтому Sandia Labs не скопировали существующую топологию на радстойкий техпроцесс (что не помогло бы само по себе), а поступили по-другому. Для обеспечения совместимости с исходным чипом полная схема разбита на относительно небольшие блоки, а схемотехника каждого из блоков перенесена на статическую КМОП-логику, более устойчивую к утечкам и сдвигу порогового напряжения транзисторов. Такой подход сохраняет взаимное расположение блоков в топологии и основные связи, упрощая и ускоряя разработку.

Для успешного редизайна был сформулирован ряд принципов.

- Блоки должны сохранять работоспособность при вариация порогового напряжения n-канальных транзисторов от 2В до почти нуля (при номинальном значении в 1 В) и p-канальных от -0.5 В до -4 В (при номинальном значении в -1 В). Это жесткие требования из-за того, что при сдвиге порогов транзисторов в разные стороны изменяется порог переключения логических вентилей и, как следствие, изменяется тайминг работы схемы, заставляя разработчика закладывать гораздо большие задержки и уменьшать частоту работы чипа.

- Впрочем, при пороге -4 В и питании 5 В p-канальные транзисторы почти не открываются, и никакие усилия дизайнера не могут спасти ситуацию, поэтому в Sandia Labs поступили брутально, увеличив напряжение питания процессора до 10 В. Брутально, но эффективно, а выгода в энергопотреблении от перехода с NMOS на CMOS так велика, что можно и потерпеть.

- Кроме этого, для преодоления негативных последствий сильного роста порога p-канальных транзисторов, в схеме везде отдавался приоритет вентилям NAND (где p-канальные транзисторы стоят параллельно) над вентилями NOR (где транзисторы стоят последовательно).

- Сдвиг порога транзисторов под дозой излучения меняется в зависимости от электрического режима, в котором находится транзистор. Это важно для разного рода согласованных пар, например, для усилителей записи и чтения памяти. Поэтому оба чипа памяти спроектированы так, что линии доступа предзаряжены постоянно, а не только тогда, когда это необходимо.

Никаких специальных мер для защиты от одиночных сбоев (типа кодирования Хэммингом или более сложных ячеек памяти) не применялось, так как моделирование показало, что повышения напряжения питания до 10 В достаточно для того, чтобы критический заряд переключения стал больше разумных значений, которые может внести ТЗЧ. Испытания подтвердили эффективность этого подхода, продемонстрировав отсутствие сбоев при питании в 10 В и их наличие при уменьшении питания до 5 В.

Итого «классический» подход к повышению стойкости на проектных нормах три микрона выглядит так: основная проблема – дозовый сдвиг порогового напряжения транзисторов, применение специально разработанной технологии – необходимость, защита от тиристорного эффекта делается технологически, от дозы – совместно на уровне технологии и низкоуровневой схемотехники, с одиночными сбоями все хорошо из-за повышенного напряжения питания. По итогам чип от Sandia Labs при полной pin-to-pin и структурной совместимости с оригиналом имел 18000 транзисторов против 6500, зато дозовая стойкость получилась выше на три порядка. В статье также отмечен важный момент: техпроцесс был полностью фиксирован до начала разработки, так как его дальнейшая оптимизация могла скомпрометировать дизайн чипа. Например, применение более тонкого подзатворного диэлектрика, рассматривавшееся тогда как основной способ повышения радиационной стойкости, из-за изменения ёмкостей затворов серьезно влияет на скорость работы элементов микросхемы.

Арсенид галлия

Изменение или даже специальное создание технологии для производства радстойких чипов было в те времена чем-то не только само собой разумеющимся, но и необходимым. Поэтому логично, что параллельно с исследованиями способов сделать кремниевую КМОП-технологию более стойкой шли и поиски альтернативных вариантов. Основным из них был арсенид галлия.

Активные исследования в области арсенида галлия шли с начала семидесятых до середины девяностых, и его высокая радиационная стойкость, вызванная отсутствием в JFET транзисторах подзатворного диэлектрика, была одним из основных драйверов этих работ. Кульминацией стал 1984 год, когда DARPA подписала целых три контракта на разработку GaAs MIPS микропроцессоров — с RCA, McDonnell Douglas и коллаборацией CDC-TI. Одним из важных требований технического задания было ограничение в 30 тысяч транзисторов, с формулировкой “чтобы процессоры можно было начать серийно производить с приемлемым выходом годных”. Кроме этого, существовали варианты конверсии на арсенид галлия семейства Am2900, версии 1802 микроконтроллеров, базовые матричные кристаллы на несколько тысяч вентилей и чипы статической памяти на несколько килобит.

Тут же можно заметить, что параллельно в 1984-1994 годах тематику GaAs развивали в СССР, на «Микроне» была создана 5600 серия со сходной степенью интеграции. Правда, если американцы пытались сделать на GaAs подобие КМОП технологии, то К5600 реализовывала намного более быструю, но сложную и прожорливую истоково-связанную логику (ИСЛ). Советские наработки по GaAs были брошены одновременно с американскими – выгоды перевешивались непомерной дороговизной из-за выхода годных, составлявшего единицы процентов. Арсенид галлия так и остался материалом будущего.

RISC-архитектуры

Страдания GaAs в США здорово продлила тогдашняя мода на RISC-процессоры, обещавшая серьезное уменьшение количества транзисторов на чипе при сходной с CISC производительностью. Разумеется, RISC-процессоры реализовывали не только на арсениде галлия, кремний тоже отлично подходит для этого. Вся «большая четверка» – ARM, MIPS, SPARC, POWER – отметилась в космосе, но во-первых, она и так всем более-менее знакома, а во-вторых, у меня будут поводы поговорить о них позже, поэтому сейчас – пример менее известной, но достаточно важной для космоса архитектуры.

В 1980 году US Air Force для удешевления и унификации программного обеспечения военной авиации издали стандарт Mil-Std-1750A, описывающий систему команд 16-битного микропроцессора. Стандарт никак не регламентирует деталей реализации, что дало разнообразным поставщикам возможность представлять собственные решения, совместимые со всеми остальными и с создаваемым в интересах USAF программным обеспечением. ПО, кстати, писалось на специальном военном языке JOVIAL (Mil-Std-1589) или на не менее специальном военном языке Ада (Mil-Std-1815A). На JOVIAL, кстати, до сих пор работает довольно много систем контроля воздушного трафика (что не так давно привело к куче проблем в Англии, после которых выяснилось, что на обучение персонала древнему языку тратится довольно много сил и денег).

Стандарт оказался довольно удачным и получил распространение не только в USAF, но и в NASA, ESA и даже в израильской военной авиации. В космосе 1750-процессоры от разных поставщиков (как в виде отдельных чипов, так и, например, из тех самых bit-slice 2901 чипов, разработанных для Galileo) управляют и управляли американскими миссиями к Марсу, миссией к Юпитеру Cassini и многими другими. В европейском космическом агентстве Mil-Std-1750A и разработанные на его основе английские чипы MA31750 производства Dynex и Plessey стали де-факто стандартом. Став знаковым явлением в развитии IT двойного назначения, стандарт 1750A был объявлен непригодным для новых проектов USAF в 1996 году, когда стало ясно, что 16 бит мало и что нужно переходить на 32-битные архитектуры, к тому времени уже устоявшиеся и прочно занявшие свое место в коммерческой электронике. В космосе смена поколений идет еще медленнее, чем в авиации, и еще очень много лет аппараты под управлением 1750А продолжали запускаться. Например, европейская Rosetta, отправленная к комете в 2004 году и успешно работавшая на орбите буквально пару лет назад, или индийская марсианская миссия “Мангальян”, запущенная в 2013.

Позднейшая история

Подробный рассказ про следующее поколение процессоров я продолжу на примере европейских разработок, так что про американские чипы только обозначу общую канву: за периодом «1802+8085» последовал период «1750+386», где 386 процессоры были также разработкой Sandia Labs по документации Intel; эти 386 летают на МКС, они же работали на Hubble после того, как на нем была проведена замена компонентов по помощи Space Shuttle. Тогда де на сцене на какое-то время появилась линейка MIPS-процессоров, из которых наиболее известен Mongoose-V, стоящий в New Horizons, а после американский рынок был де-факто монополизирован процессорами RAD, построенными по архитектуре POWER. Эти процессоры управляли марсоходами Phoenix, Opportunity, Spirit и Curiosity, телескопами Spitzer и Kepler – и вообще всем, что запускается в NASA последние двадцать лет. Последнее поколение – RAD5500 – было сертифицировано для космоса в 2016 году и должно отправиться в первый полет буквально со дня на день. Последнее – потому что сейчас идёт новая программа HPSC (High Performance Spaceflight Computing), в рамках которой Boeing выиграл тендер на разработку многоядерного ARM-процессора, который должен в будущем стать единой вычислительной платформой для космических аппаратов NASA и USAF. Примечательно, что многоядерность и разделение ресурсов позволит управлять частью приложений с помощью ОС реального времени (RTEMS в данном случае), а тем, что реального времени не требует – при помощи Yocto Linux.

Завершая первую часть, отмечу, что американцы до последнего держатся за проверенный временем подход конверсии гражданских дизайнов в космические путем их переноса на специально разработанные технологические процессы – HPSC будет, кажется, первым проектом, разработанным с нуля. Упомянутый выше Mongoose-V – это коммерческое ядро MIPS на радстойком базовом матричном кристалле, а набор масок для первого поколения RAD6000 изготавливали из тех же файлов топологии, что и обычные PowerPC601. При этом прогресс в технологии постепенно смещал фокус с одних видов радиационных эффектов на другие, ведь с уменьшением проектных норм снижается толщина диэлектриков, а с ней и сдвиг порога транзисторов; параллельно уменьшение проектных норм приводит к снижению напряжения питания и уменьшению энергии переключения вентилей. Вместе это означает, что получить приемлемую стойкость к дозе излучения стало намного проще, зато одиночные сбои из юпитерианской экзотики уже к середине девяностых превратились в главную головную боль разработчиков, потребовавшую принципиально других подходов к проектированию микросхем.

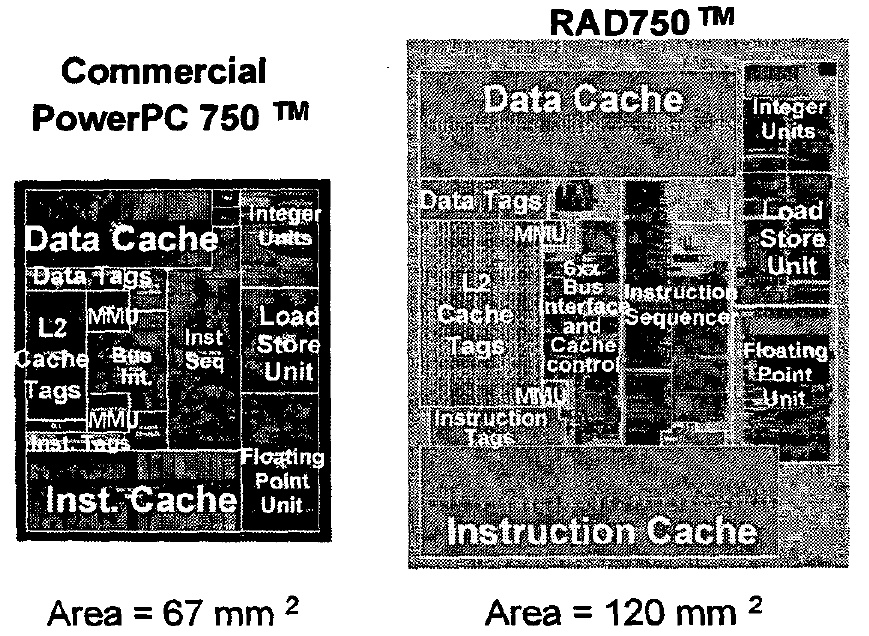

Рисунок 6. Сравнение кристаллов PowerPC750 и RAD750. Чипы выполнены на одинаковых проектных нормах, их площадь при этом различается почти в два раза. Обратите внимание на практически идентичную планировку блоков – вот что происходит, когда обеспечивается совместимость на низком уровне. Огромные различия в размерах блоков памяти заставляют предположить использование многотранзисторых (10Т вместо 6Т) радстойких ячеек памяти с встроенным резервированием.

Смена парадигмы – на примере Европейского космического агентства

История европейского космического процессоростроения неразрывно связана с именем шведского инженера Йири Гейзлера (Jiri Gaisler). Он пришел в ESA в середине восьмидесятых и начал заниматься разработкой первых собственных европейских микропроцессоров космического назначения. Сперва это были лицензированные американские 1750A, потом собственные разработки на базе той же системы команд (производившиеся в Англии) – для сохранения совместимости с уже написанным софтом. И, раз уж здесь айтишный сайт, давайте посмотрим, какой это софт:

Proprietary tools

Ada compiler from TLD (USA)

Open source

The GNU compilation system for the 1750 was initially composed of two main parts.

a set of tools developed by CNS under the Agency’s contract:

- GNU C compiler (gcc-2.7.2)

- Linker, assembler, archiver, etc (binutils-2.7)

- Standalone C library

- POSIX-Threads library (IEEE 1003.1c-1995) (a preemptive real time executive)

- GNU Debugger (gdb-4.16) for the 1750

a set of tools either developed internally in the Agency or available from external sources, and namely:

- CRTX (the SmartCom small cyclic/synchronous real time executive – external)

- Standalone 1750 simulator (O. Kellogg sim1750-2.3b – external)

- wxIDE (a portable Integrated Development Environment based on J. Smart wxWindows 2.65 – internal)

Важный момент, отличающий работу Европейского космического агентства в части ПО – это целенаправленная и систематическая поддержка и оплата создания open source продуктов, а также создание экосистем для переиспользования разработок и снижения затрат. Не только для софта: для радстойких микросхем бельгийский институт IMEC создает и поддерживает в интересах ESA платформы разработки DARE (Design Against Radiation Effects), включающие маршруты проектирования, адаптированные PDK и большие наборы цифровых и аналоговых IP-блоков на шести разных техпроцессах (350, 180, 90 и 65 нм). Платформы эти не опенсорсные, но лицензируются при необходимости всем исполнителям контактов ESA.

ERC32 – первый полностью европейский

А теперь вернемся к Йири Гейзлеру. Первое поколение собственных европейских процессоров по архитектуре 1750A (трехчиповый комплект был завершён в 1989 году, полностью интегрированный MA31750 в 1991) разрабатывалось с прицелом на миссию “Розетта”, которая должна была стать одним из флагманов широкой европейско-американской научной программы, включавшей также телескоп “Хаббл” и миссии по изучению Солнца и планет.

“Розетта” – аппарат с длинной и сложной судьбой. Проект стартовал в 1986 году, совместно с США и должен был переиспользовать множество частей аппаратов Mariner MkII (отсюда растут ноги у применения 1750A), однако через некоторое время конгресс США отменил финансирование американской части программы (позднее переделанной под меньший бюджет в зонд Cassini), и Европа осталась сама по себе. В 1994, когда стало понятно, что изначальную миссию, включавшую доставку кометного вещества на Землю, в одиночку не потянуть, задачи миссии были переформулированы; еще через десять лет, в 2004 году “Розетта” начала свой путь к комете Чурюмова-Герасименко, а в 2014, когда она ее достигла, в новостях можно было прочитать в том числе и про древние микросхемы с производительностью карманного калькулятора. И это еще в новостях недостаточно много писали про стоявшие в посадочном модуле Philae стековые процессоры, аппаратно реализовывавшие язык Forth.

Судьба “Розетты” наглядно показала ESA, что зависеть от американских партнеров – не самая лучшая идея, и агентство начало вкладывать довольно много денег в программы достижения технологической независимости или, по-нашему, в импортозамещение. Спустя тридцать лет эти программы продолжают активно существовать, получив относительно недавно новый импульс, связанный с желанием Европы иметь доступ на российский и, что более важно, на китайский космический рынок независимо от американских экспортных ограничений, санкций и торговых войн США с Китаем.

Накопив достаточно опыта, команда ESA взялась за более амбициозную задачу: 32-разрядный процессор. В то время ещё было модно придумывать собственные RISC-архитектуры, но денег на такие развлечения ESA не выделила, предложив разработчикам выбрать какую-то из уже существующих ISA, причем непроприетарных и желательно с хорошей софтовой экосистемой. Выбор после некоторого изучения и последующего обсуждения с парой десятков потенциальных подрядчиков ESA пал на SPARC, обладающую всеми нужными качествами и уже в начале девяностых свободно распространяемую солидным консорциумом, ведомым Sun и Fujitsu. Смешной факт: ARM рассматривалась, но была отвергнута по причине малого количества софта. В числе других интересных требований к процессору была аппаратная поддержка языка Ада для ускорения работы уже написанного для 1750A софта, а также наличие VHDL-моделей для ускорения разработки систем на основе процессора.

Принципиально новым пунктом требований к разработке было то, что разрабатывался не собственно микропроцессор как чип, а высокоуровневая модель процессора на языке VHDL. Это было сделано для того, чтобы не зависеть от конкретного производителя микросхем и обеспечить доступность процессора на много лет вперед, даже в случае, если с выбранной фабрикой что-то случится. По американской традиции, дизайн ядра был основан на коммерческом процессоре Cypress CY601, а за радиационную стойкость отвечала французская фабрика Temic Semiconductor (радстойкий объемный техпроцесс с проектными нормами 800 нм). Вместо запланированных трёх лет проект продлился пять (1992-1997), дизайн был финализирован на десятой (!) итерации тестовых чипов, от поддержки Ада пришлось отказаться – но по итогам проект был признан успешным. Получившийся дизайн назвали ERC32, трехчиповый микропроцессорный комплект вышел на рынок под названиями TSC691-693, а еще позже проект был выполнен на одном кристалле как TSC695 (20 MHz, 14 MIPS, 4 MFLOPS, 0.5 W).

В дополнение к обычной реализации SPARC, в ERC32 реализовано обнаружение сбоев и их программное исправление. 99% триггеров в регистрах Integer Unit, 100% триггеров в FPU и внешние шины снабжены контролем четности. Обнаруженные ошибки вызывают шесть типов прерываний, реакция на которые определяется программно. В простейшем случае обработка прерывания заключается в повторе сбоившей инструкции, в худшем варианте это может быть перезапуск бортового компьютера. Кроме этого, инструкция NOP модифицирована таким образом, что вместо ничего не делания она проверяет контрольную сумму, получаемую как XOR опкодов всех предыдущих инструкций. Если сумма не совпадает с ожидаемым значением (полученным при компиляции), также вызывается прерывание. Заканчивая описание ERC32, замечу, что в нем совсем нет кэш-памяти, то есть эту большую проблему разработчики процессора спихнули на других людей.

Предложенные меры по детектированию сбоев привели к росту площади на 15%. Или на 130%, если рассматривать включение двух ERC32 в дублированной конфигурации, для которой тоже была аппаратная поддержка.

ERC-32 и российский сегмент МКС

Первый прибор, использовавший ERC32, несомненно заслуживает отдельного рассказа, так как это был первый случай использования иностранного блока в российской mission-critical аппаратуре, а также потому, что он наглядно показывает, как не надо делать важные проекты.

В 1992 году, в связи с очередными сложностями в постройке американско-европейской долговременной космической станции «Freedom», ESA инициировала переговоры о возможности своего участия в проекте российской орбитальной станции «Мир-2». Российская сторона была согласна, но с бюджетом в 1992 году и у нее было не очень. После двух лет напряженных переговоров (голосование в конгрессе США закончилось со счётом 216-215) проекты «Мир-2» и «Freedom» превратились в Международную космическую станцию (МКС), какой мы ее знаем сегодня. Европейско-российские договоренности тем временем остались в силе, и ESA начало проект системы обработки данных для российского модуля “Заря” (DMS-R, Data Management System – Russian).

Доступные в 1995 году процессоры – радстойкие 1750 и 386 – не удовлетворяли требованиям по производительности, а в нагрузку к RAD6000 нужно было купить целые процессорные платы, что не давало гибкости в разработке. Ещё одним вариантом был ERC32, но он к тому моменту существовал только в виде моделей, и ещё не было сделано ни одного тестового чипа в кремнии. Я не знаю, что двигало этими людьми, но это были явно не мыли о том, что с несуществующим перспективным процессором что-то может пойти не так. А с ним, разумеется, произошли отставание от графика (которое некоторое время обходили, используя для разработки ПО коммерческие аналоги) и море багов (что было предсказуемо для первого большого проекта небольшой команды разработчиков), причем баги были плохо документированы, даже при условии постоянного прямого контакта разработчиков DMS-R и разработчиков ERC32. Один из багов в FPU, который разработчики из РКК «Энергия» никак не могли локализовать, в итоге пришлось обходить при помощи патчей в операционной системе.

Дальше были ещё задержки (в 1998 году с финансированием космоса в России опять стало не очень), но в 2000 году разработанные ESA бортовые компьютеры были успешно выведены на орбиту и с тех пор работают внутри российского блока «Заря».

Рисунок 7. Бортовой компьютер модуля МКС “Заря” на основе процессора ERC32.

В 1996 году, ещё до окончания проекта ERC32, началась разработка требований к его наследникам. Аппетиты программистов выросли до 100-500 MIPS вместо 10, а оглушительный успех исходного проекта означал, что Европа в обозримом времени будет продолжать работать с архитектурой SPARC. Первоочередной задачей было создание однокристальной версией ERC32, перспективной – новое процессорное ядро.

LEON-FT

Главной особенностью проекта LEON-FT стала изначальная задача создать не конечный продукт в виде чипа, а лицензируемое ядро в виде vhdl-кода, и обеспечение сбоеустойчивости (fault tolerance) вместо радиационной стойкости (radiation hardness). Опыт ERC32 показал, что для надёжной работы ему требуется дублирование, и логичным следующим шагом была разработка системы, не нуждающейся в нем. Решение этой задачи потребовало не только обнаружения, но и исправления сбоев на аппаратном уровне, без задействования ПО. Идеи fault tolerance и radiation hardening by design придумали, разумеется, не авторы LEON-FT, но до них этот подход в основном рассматривался на транзисторном уровне, а они первыми полностью отвязали борьбу с одиночными сбоями от физической реализации чипа и сделали целью проекта создание стойкого чипа на коммерческой технологии, причем на любой доступной в конкретный момент я решив таким образом проблему устаревания техпроцессов и закрытия фабрик. Таким образом, был зафиксирован сдвиг парадигмы: за двадцать лет до того, как мы видели на примере чипов SA3000, основной проблемой была полная доза радиации, с которой боролись технологическими методами, а одиночные сбои рассматривали по остаточному принципу. К 2000 году фокус изменился, одиночные сбои стали основной проблемой, а привязка к конкретной технологии стала рассматриваться как недостаток, а не как достоинство, даже если фабрика была проверенной и надёжной. К слову, сейчас английский (и ни слова о Brexit) Dynex Semiconductor принадлежит китайцам, а французский Temic стал частью американского Microchip.

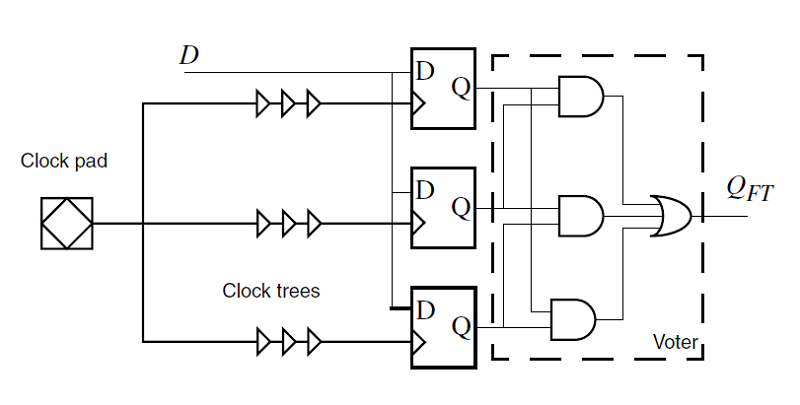

Ядро LEON-FT было написано на VHDL и снабжено конфигуратором, позволяющим выбрать разные варианты защиты от одиночных сбоев для разных частей чипа: для регистрового файла и кэш-памяти (появилась кэш-память!) один/два бита четности или код Хэмминга а также форсирование кэш-промаха, для триггеров в datapath наличие или отсутствие тройного резервирования, для конвейера (появился конвейер) – возможность сброса и повтора с началом от сбойной инструкции. Таким образом, единственная зависимость от физической реализации – только в особенностях интерфейса с заказными блоками памяти, составляющими регистровый файл. Рост площади ядра с максимальной защитой без учёта кэшей – около 100%, с учётом – около 40%; со всеми отключенными опциями получилось просто ядро SPARC V8, выпущенное в Open Source как LEON (без приставки -FT). В дальнейшем эта практика продолжилась, и последующие версии LEONx в нестойкой версии выкладывались в открытый доступ, а конфигурируемые сбоеустойчивые варианты LEONx-FT лицензировались за деньги для создания микросхем или как Soft IP для зашивки в ПЛИС. И действительно, так как LEONx-FT никак не привязаны к технологии, ничего не мешает использовать их в ПЛИС – конечно, при соблюдении (довольно жёсткого) условия отсутствия сбоев в памяти, управляющей соединениями элементов на кристалле. Впрочем, если эта память – не SRAM, а флэш или EEPROM, то это вполне реалистичная идея, даже без учёта существования сбоеустойчивых ПЛИС, в которых конфигурационная память аппаратно покрыта самокорректирующимися кодами.

Рисунок 8. Троированный триггер.

Заметка на полях о дизайне библиотек: для совместимости с любыми библиотеками, элемент голосования здесь собран из обычных логических вентилей. Сам он, разумеется, никак не защищен от одиночных сбоев, но он намного меньше, чем обычный триггер, а значит вероятность попадания в него ниже, и сбой короткий, а не защелкивается. Если же этого недостаточно, то существуют специальные реализации элемента голосования на транзисторным уровне, более устойчивые к сбоям, чем представленный на рисунке вариант, и их можно добавить в библиотеку как примитивы. На проектных нормах 1000-100 нм возможно довольно много интересных реализаций логических элементов с повышенной сбоеустойчивостью, позволяющих минимально менять логический дизайн микросхемы и не внедрять сложные троированные конструкции. Самые популярные варианты – внутреннее дублирование в элементах и встроенная фильтрация (например, в виде резисторов в цепях обратной связи в памяти).

Рисунок 9. Ячейка памяти DICE со встроенным дублированием; из-за перекрестных обратных связей сбой в ней возможен только при одновременном попадании в два инвертора, которое относительно легко предотвратить. Справа – топологии обычной ячейки памяти и DICE.

LEON-FT был тестовым проектом и не предполагался к коммерциализации; эту разработку, как и последующие коммерческие продукты – ядра LEON2-FT – Гейзлер делал уже в собственной компании Gaisler Research, расположенной в Гётеборге. Эксклюзивные права на LEON2-FT получила фирма Atmel, купившая выпускавшую ERC32; получившийся продукт – широко известный в том числе в России чип AT697, выполненный на специальном радстойком техпроцессе Atmel и, в силу того, что Atmel – американская компания, подверженный экспортным и санкционным ограничениям. В 2008 году Gaisler Research был продан американцам же из Aeroflex, потом их купил английский Cobham, потом начался Brexit, а теперь уже Cobham под вой о недопустимости разбазаривания национального достояния и национальной обороны покупает какой-то американский инвестор. Такая вот история импортозамещения и технологической независимости в Европе.

Текущая версия – LEON5 – имеет восьмистадийный конвейер, предсказатель ветвлений и прочие черты современных микропроцессоров, а начиная с третьей версии, Gaisler предлагает не только процессорные ядра, но и большую библиотеку разнообразных IP-блоков, позволяющую пользователям создавать системы на кристалле, подходящие для их специфических требований, а также довольно широкий набор собственного, стороннего и open source ПО (подробное описание можно найти здесь, операционные системы включают VxWorks 6.9 и 7.0, RTEMS 4.10 и 5, а также Linux на основе kernel 3.10 и 4.9).

Разделение труда

Как я уже говорил выше, IP-ядра LEONx-FT решают только проблему одиночных сбоев; защита от полной дозы и тиристорного эффекта возлагается на пользователя, который должен подобрать или стойкую FPGA, или комбинацию из технологии и библиотек. Рассмотрим подробнее на примере чипа Gaisler GR712, использованного в недавней израильской лунной миссии «Берешит».

Имеются три уровня реализации. На верхнем уровне GR712 – это двухядерный процессор LEON3-FT. На уровне производства – никак не модифицированный коммерческий техпроцесс 180 нм израильской фабрики TowerJazz. Между ними – набор радиационностойких библиотек RadSafe, разработанный израильской же компанией Ramon Chips (названной в честь астронавта Илана Рамона, погибшего в катастрофе «Коламбии»). Именно библиотеки RadSafe обеспечивают за счёт схемотехники и топологии базовых логических элементов отсутствие тиристорного эффекта и стойкость к полной поглощённой дозе радиации. Аналогичным образом GR716 – микроконтроллер LEON3-FT – создан в партнёрстве с IMEC, предоставившими логические библиотеки и аналоговые IP для техпроцесса 180 нм тайваньской фабрики UMC. GR740 – процессор, реализующий четырехядерный LEON4-FT – сделан на 65 нм технологии ST Microelectronics, предоставившей радстойкие библиотеки для своего процесса. Как видите, привязки к технологии действительно нет никакой, и можно свободно выбирать партнёров для физической реализации в зависимости от того, какую задачу нужно решить с конкретным чипом.

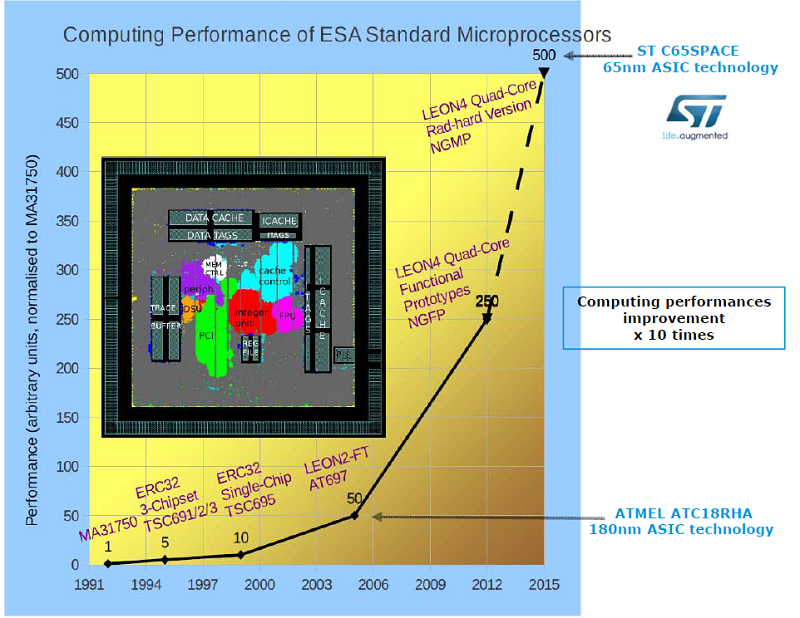

Рисунок 10. Краткая история развития европейских радстойких чипов, от MA31750 до прототипов того, что стало процессором GR740 (техпроцесс 65 нм STM, четыре ядра, 250 МГц, 459 MIPS/ядро, 22.7 MFLOPS).

Суммируя эту часть, хочу ещё раз подчеркнуть несколько тезисов. Во-первых, уменьшение проектных норм привело к тому, что сильно повысилась важность одиночных сбоев в обеспечении радиационной стойкости, и это потребовало пересмотра подходов к разработке микросхем. Во-вторых, уменьшение проектных норм также привело к сильному удорожанию производства и сокращению числа игроков на рынке, и стала необходимостью разработка радстойких микросхем на обычных коммерческих технологиях, что было принципиально невозможно на раннем этапе. В-третьих, усложнение дизайнов микросхем и ПО для них привело к необходимости максимального переиспользования имеющихся заделов (не только космических), а также создания и поддержки экосистем разработки, объединяющих усилия большого количества компаний.

Как реализовывались и развивались эти требования – посмотрим послезавтра во второй части на примере современных российских разработок. В ней же будут небольшие рассказы про остальные страны, занимающиеся радстойкими микросхемами, а также про то, что ждет индустрию в ближайшем будущем.