Сегодня стартует ежегодный двухдневный саммит Flash Memory Summit (2018). В преддверии этого события китайская компания Yangtze Memory Technologies (YMTC) раскрывает детали широко анонсированной фирменной технологии Xtacking. Как было заявлено, Xtacking изменит представление о скорости работы интерфейсов 3D NAND и логики, управляющей внутренними процессами в микросхемах 3D NAND. Чем же это достигается?

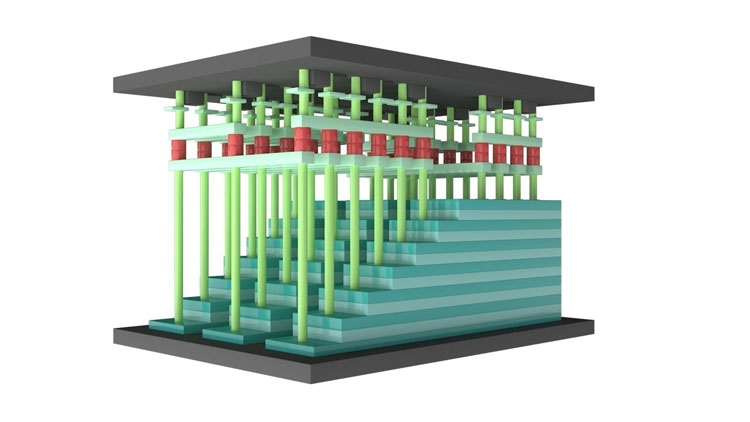

«Китайская память» 3D NAND состоит из двух отдельных кристаллов с интерфейсом и массивом памяти (стык в месте «красных» контактов)

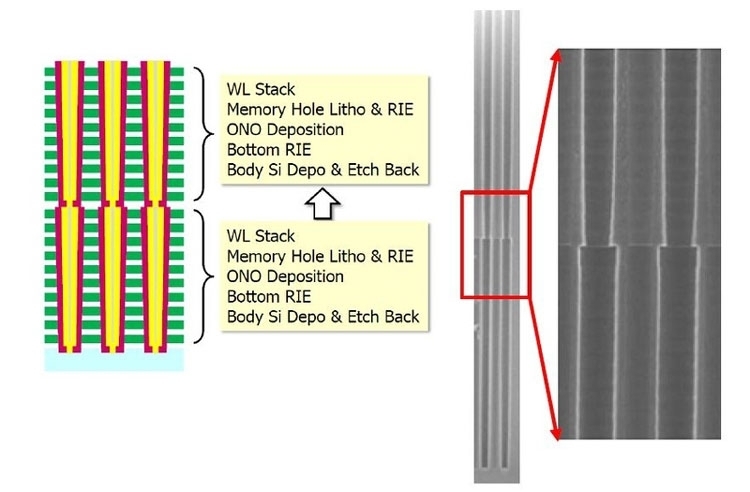

Китайский производитель 3D NAND предлагает выпускать управляющую массивом памяти NAND-флеш логику и сами массивы на разных пластинах с использованием совершенно отличающихся техпроцессов. Сегодня все производители 3D NAND выпускают чипы многослойной памяти в виде монолитных 3D-структур в одном технологическом цикле обработки пластин (за исключением случая, когда необходимо удвоить количество слоёв, тогда 64-слойные и 96-слойные микросхемы производятся в виде стеков из 32- и 48-слойных компонентов).

96-слойная 3D NAND может быть составлена из двух 48-слойных кристаллов 3D NAND (International Memory Workshop 2018)

В любом случае, управляющая логика и периферийные интерфейсы 32–96-слойных «классических» микросхем 3D NAND расположены на одном кристалле с массивом памяти. Китайцы предлагают отделить «мух от котлет» и выпускать отдельно логику с интерфейсами и массивы памяти — в виде двух отдельных кристаллов и лишь затем соединять их вместе. Зачем такие сложности, когда весь мир обходится монолитным техпроцессом производства 3D NAND?

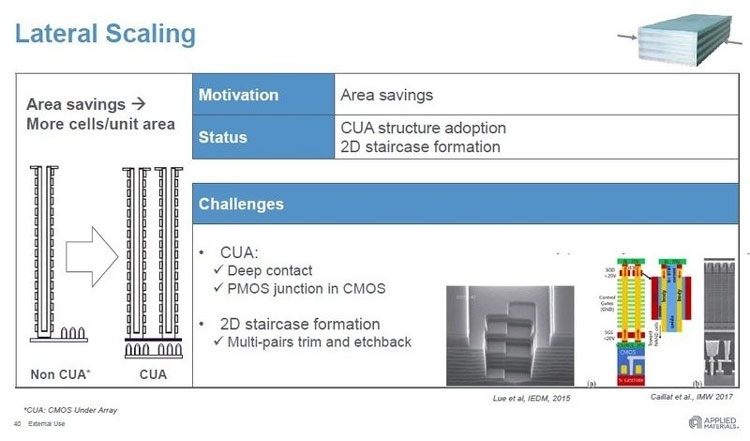

По словам китайских разработчиков, размещение логики и интерфейсов на одном кристалле с массивом памяти уже сегодня отбирает у микросхем памяти 20–30 % и так дефицитной площади. С появлением 128-слойных чипов площадь под логику и интерфейсы увеличится до 50 % от площади кристалла. Это отрицательно скажется на себестоимости, хотя мировые лидеры производства 3D NAND придумали, как частично обойти это препятствие — перенесли логику под массив памяти (технология CMOS under the array, CuA). Китайцы же сделали это радикально — вообще разнесли логику и массив памяти по двум разным кристаллам, которые затем электрически соединяются через систему вертикальных соединений на нижних поверхностях каждого из них (Vertical Interconnect Accesses, VIAs). Подчеркнём, это не TSVs соединения, которые более сложные в производстве и имеют много меньший диаметр. Но это также даёт модульный подход, позволяя разработчикам сократить до 3 месяцев на разработке новых флеш-продуктов.

Наглядно о технологии CMOS under the array (CuA)

Кроме увеличения плотности памяти NAND производство логики с интерфейсами и массива памяти с использованием различных техпроцессов даёт следующий эффект. Логику и интерфейсы можно выпустить с использованием более тонкого и, следовательно, более производительного и энергоэффективного техпроцесса. Это позволило YMTC более чем в два раза увеличить скорость обмена с памятью по каждому контакту. Так, если интерфейс Toggle DDR 4.0 даёт 1,4 Гбит/с, то реализация технологии YMTC Xtacking обещает скорость обмена до 3 Гбит/с — это скорости интерфейса DRAM DDR4. Впечатляет! Другой вопрос, сможет ли массив памяти NAND поддержать эту скорость? Очевидно, для окончательных выводов нам придётся ждать появления «китайской» памяти на рынке. Второе поколение технологии Xtacking в виде 64-слойной 3D NAND будет внедрено в производство только в 2019 году.

Источник: 3DNews