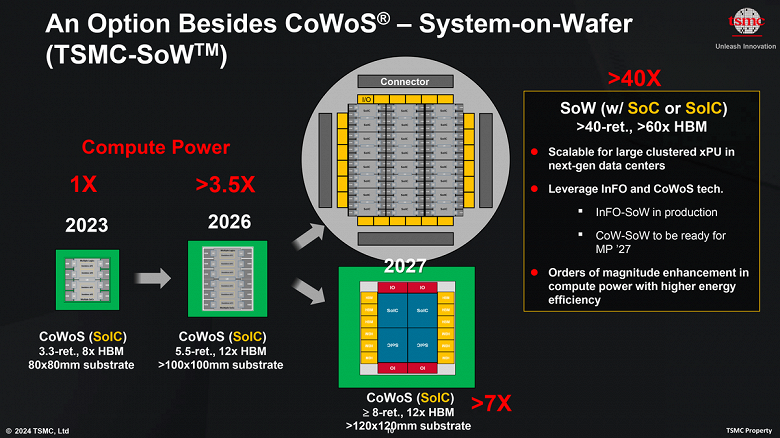

Компания TSMC уже через несколько лет сможет выпускать гигантские чипы, которые будут превосходить текущих рекордсменов более чем вдвое.

Новая версия технологии упаковки CoWoS позволит TSMC уже через два-три года выпускать чипы с корпусами размером 120 х 120 мм!

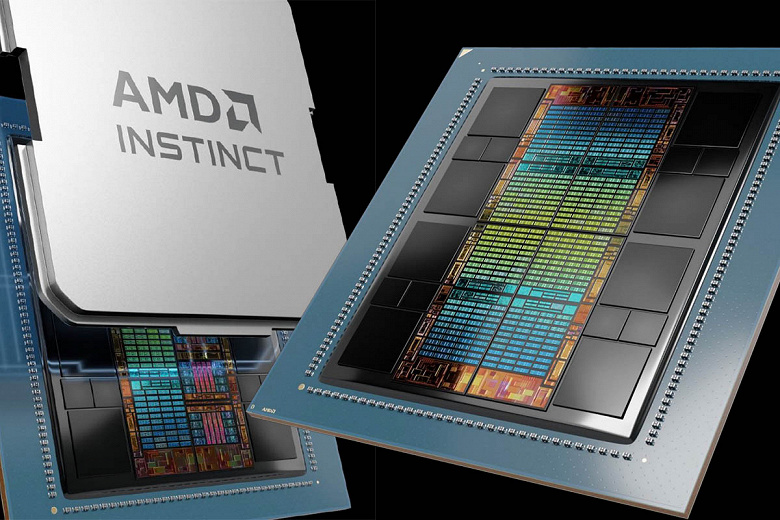

Актуальная технология CoWoS позволяет TSMC создавать кремниевые вставки, размер которых примерно в 3,3 раза больше размера фотомаски. Таким образом, непосредственно сам CPU или GPU, восемь стеков памяти HBM3/HBM3E, чиплеты ввода-вывода и другие могут суммарно занимать до 2831 мм2 при максимальном размере подложки 80×80 мм.

Следующее поколение CoWoS_L, которое должно быть готово к производству в 2026 году, будет способно использовать интерпозеры, размер которых примерно в 5,5 раз превышает размер сетки. То есть для набора чипов будет доступна площадь в 4719 мм². Для таких SiP также потребуются подложки большего размера, и, судя по слайду TSMC, речь идёт о размерах 100×100 мм.

Уже в 2027 году TSMC сможет создавать чипы с подложкой 120х120 мм и доступной площадью в 6864 мм2. Учитывая, сколько потребляют современные чипы с кратно меньшими размерами, можно предположить, что такие монстры будут требовать несколько киловатт энергии.

Конечно, до размеров и потребления чипов Cerebras, которые фактически занимают всю 300-миллиметровую кремниевую пластину после обрезки её до квадратной формы, оговариваемым решениям TSMC далеко, но Cerebras представляет собой уникальное специализированное решение, а новая версия CoWoS позволит создавать монструозные чипы для самых разных задач.

Источник: iXBT