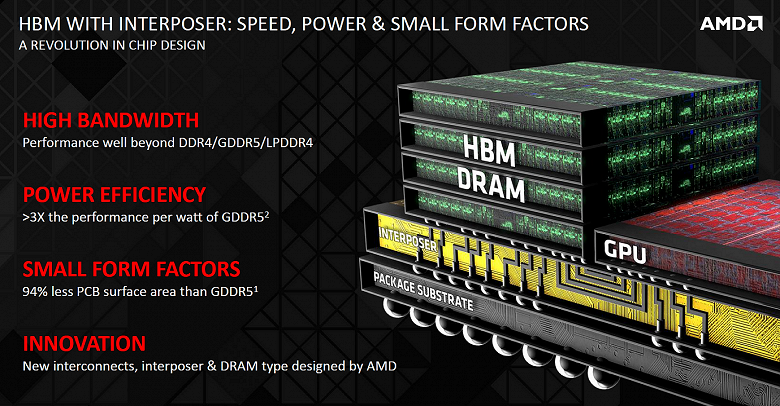

Организация JEDEC Solid State Technology Association, разрабатывающая стандарты для микроэлектронной промышленности, объявила о публикации обновления стандарта DRAM JESD235 High Bandwidth Memory (HBM) DRAM. Память HBM DRAM используется в графических приложениях, суперкомпьютерах, серверах, сетях и клиентских приложениях, где пиковая пропускная способность, пропускная способность в расчете на потребляемую мощность и емкость в расчете на площадь кристалла являются важными показателями. Стандарт был разработан и обновлен при поддержке ведущих разработчиков графических процессоров и центральных процессоров для расширения кривой роста пропускной способности системы за пределы уровней, поддерживаемых традиционной памятью в отдельных корпусах. Спецификация JESD235B доступна для скачивания на сайте JEDEC .

Стандарт JEDEC JESD235B HBM закрепляет использование широкой шины ввода-вывода и межкристальных соединений (TSV) для поддержки объема до 24 ГБ на устройство и скоростей до 307 ГБ/с. Шина шириной 1024 бита разделена на восемь независимых каналов в каждом стеке DRAM. Стандарт предполагает поддержку стеков DRAM с 2, 4, 8 и 12 уровнями TSV при полной пропускной способности, чтобы обеспечить гибкость системы по части объема стека, который может лежать в пределах от 1 ГБ до 24 ГБ.

Обновление расширяет полосу пропускания до 2,4 Гбит/с на каждый вывод, добавляет новую опцию компоновки для конфигураций с плотностью слоя 16 Гбит и 12 слоями, и обновляет параметры полиномиального регистра (Multiple Input Signature Register, MISR) для этих новых конфигураций. Кроме того, сделаны некоторые уточнения, касающиеся тестовых функций и совместимости между компонентами HBM разных поколений.

Источник: iXBT