Следующий большой шаг в обеспечении радиационной стойкости наступил с переходом на суб-100 нм, где практически каждое следующее поколение технологии приносит новые вопросы: меняются материалы, меняются требования к топологии, растет статическая мощность (утечки безо всякой радиации, которые под дозой становятся еще хуже), продолжает расти значимость одиночных эффектов, которые превращаются во множественные. Эти задачи потребовали разработки новых подходов и, что удивительно, частичного возврата к старым, потому что часть вещей, отлично себя зарекомендовавших на нормах 1-0.18 мкм, на более тонких нормах не работает. Например, в таких технологиях для повышения выхода годных запрещено делать любимые дизайнерами радстойких чипов кольцевые транзисторы. О том, как дизайнеры справляются с новыми вызовами, я расскажу на примере России – и заодно сравню достижения наших соотечественников с успехами иностранных коллег и покажу, чего стоит ожидать в обозримом будущем.

Современность – на примере России

Я выбрал Россию для иллюстрации современного этапа не потому, что российские разработки чем-то выделяются на мировом уровне, а потому, что про что-то более старое писать бессмысленно. В СССР было много крутых микросхем, но вся информация об изделиях двойного назначения была засекречена, и сейчас без формы допуска можно найти только байки вида «после аварии в Чернобыле к разработчикам роботов для разбора завалов приехал лично Горбачев на чорном вертолете и привез радстойкий микропроцессор ВМ6» (на самом деле ключевые слова «сохраняет работоспособность в широком диапазоне воздействия механических, климатических и других факторов» содержатся в описании не «ххххВМ6», а 1806ВМ2). Бывают случайные мелочи: в комплекте 1839 серии, по имеющимся интервью разработчиков создававшейся для промышленных нужд, есть чип Н1839ВЖ2 – элемент голосования. В обычных компьютерах мажоритарный элемент ни для чего не нужен, но если немного погуглить, можно выяснить, что 1839 серия стоит в бортовых компьютерах спутников «ГЛОНАСС-М». Жаль только, что такое количество данных не позволяет ничего написать. Кроме того, к моменту появления радстойких микропроцессоров СССР уже плотно встал на путь копирования западных разработок, так что особенных инноваций ожидать все равно не приходится.

Девяностые в микроэлектронике прошли под знаком выживания и выжимания последних соков из советского наследия. Условный перелом наступил в 2003 году, который выдался богатым на события: в НИИСИ РАН была запущена собственная фабрика с проектными нормами 500 нм, на “Ангстреме” пошли в серию первые процессоры семейства “Мультикор”, была основана компания “Цифровые решения”, в бывшем до того дистрибьютором “Миландре” открыли дизайн-центр. Дальше случилась Федеральная целевая программа «Развитие электронной компонентной базы и радиоэлектроники» на 2008-2015 годы, не достигшая заявленных целей (45 нм к 2015 году, объем продаж 300 миллиардов рублей и т.д. и т.п.), но все же сумевшая серьезно помочь российской микроэлектронике. Прямо сейчас в России приблизительно 150-200 дизайн-центров, занимающихся разработкой интегральных микросхем, от гигантов типа “Микрона” до команд из пяти-шести человек, занимающихся нишевыми вещами. Подавляющее большинство этих команд так или иначе работает с госзаказом и создает продукты двойного назначения. При этом десятилетие между 2003 и 2014 годами прошло не только в разработке новых российских микросхем и попытках преодоления уже катастрофического разрыва с зарубежными производителями; более сложной задачей, чем создать новые микросхемы, стала задача убедить производителей систем начать их применение. Системщики же после исчерпания советского задела в большинстве плотно пересели на импортные компоненты, которые были лучше сделаны, лучше документированы, более надежны, более доступны – в общем, действительно не было причин поступать иначе. Дальше – заколдованный круг из обратной совместимости и переиспользования имеющегося задела, благодаря которому подтянувшиеся отечественные разработки все равно продолжили оставаться за бортом. Справедливости ради, среди производителей бортовой радиоаппаратуры были и есть компании, принципиально и последовательно сотрудничающие с отечественными разработчиками электронных компонентов, но в целом ситуация в отрасли выглядела примерно так:

Цитата из интервью Николая Тестоедова, директора крупнейшего российского производителя космических аппаратов ИСС имени Решетнева:

– На военных спутниках связи «Благовест» большая доля зарубежных составляющих?

– Там соотношение тоже было не очень удачное, потому что до 2014 года, когда еще не было ни рисков, ни ограничений, мы закупили большое количество иностранных комплектующих. Сроки создания спутников для Минобороны были важнее.

Кажется, я чего-то не понимаю в определении слова «риск». Зато раз в военных аппаратах можно применять импортные комплектующие, мы можем предположить, что «закладки» в микросхемах или не существуют, или отваливаются во время запуска из-за перегрузок.

Резкая перемена наступила в 2014 году, когда из-за санкций хорошие импортные микросхемы двойного назначения совершенно неожиданно стали недоступны. Тут, казалось бы, был отличный момент, чтобы собраться и перейти на отечественные разработки, но вместо этого российская микроэлектроника вновь встала на скользкие рельсы копирования или, как теперь говорят, импортозамещения. Впрочем, я слишком увлекся лирикой, поэтому давайте добавим ее еще и перед тем, как посмотреть на суб-100 нм проектные нормы, коротко посмотрим на состояние дел в российских космических микропроцессорах и микроконтроллерах по итогам десяти лет развития и пяти лет импортозамещения.

Зоопарк

Пока в США наблюдается де-факто монополия Power, а в Европе – SPARC, в России расцвели все цветы на всех архитектурах.

- ARM: три модели радстойких микроконтроллеров на базе ядер Cortex-M0 и Cortex-M4F производит «Миландр», ещё один Cortex-M0 – альянс «Ангстрема» и «Цифровых решений», и ещё три Cortex-M4F – НИИИС.

- MIPS: «MIPS-совместимые» ядра RISCore32 управляют четырьмя гетерогенными радстойкими процессорами «Мультиборт» разработки НПЦ «Элвис»; «MIPS-подобные» ядра КОМДИВ стоят в разработках НИИСИ, НИИИС и НИИМА «Прогресс».

- SPARC: головной исполнитель ОКР по разработке российского LEON4 (1906МВ016) – воронежский НИИЭТ. Интересно, что Московский центр SPARC-технологий (МЦСТ) ни при чем. Видимо, имеющийся у воронежцев опыт проектирования радстойких чипов оказался важнее.

- AMCS-96: вообще MCS-96 – это 16-битная архитектура, но сумрачные воронежские гении из НИИЭТ сделали для нее 32-битное расширение и собрали на нем радстойкий микроконтроллер.

- PowerPC (почти есть): существует чип от НТЦ “Модуль”, у которого не заявлена радстойкость, но который предназначен для “бортовой аппаратуры”. Видимо, для авионики.

Кроме этого, есть несколько 8- и 16-битных микроконтроллеров, некоторый выбор DSP/VLIW (своих и чьих-то «аналогов»), и далее практически все что угодно: память, БМК, FPGA, FPAA, АЦП, ЦАП, СВЧ, дискретные приборы. Какие-то микросхемы космического применения есть практически на любой вкус – но дело в том, что нужны не какие-то, а конкурентоспособные, хорошо документированные и хорошо поддерживаемые, а со вторым и третьим пунктами у российских производителей все традиционно было (да и есть, чего уж там) плохо.

Рисунок 11. Ещё ремарка к вопросу о разнообразии отечественных микропроцессоров: вот так обычно выглядит “импортозамещенный” процессорный модуль. Флагом “у нас отечественный процессор” помахали, а дальше продолжаем в обычном режиме. Это же фото в принципе можно использовать как иллюстрацию масштабов того, сколько всего необходимо импортозамещать.

Если производить чипы за рубежом, то прямо сейчас для продукции, про которую вы не заявляете, что она двойного назначения нет ни рисков, ни ограничений, и можно запускаться на чем угодно. Для производства в России сейчас доступны технологии с проектными нормами до 90 нм, однако «рабочие лошадки» для радстойких чипов большинства российских разработчиков – 180 нм объемная технология «Микрона» и их же 240 нм КНИ-процесс. У фабрик, впрочем, тоже полно проблем с санциями из-за импортных расходных материалов и оборудования, но это отдельная длинная и печальная история.

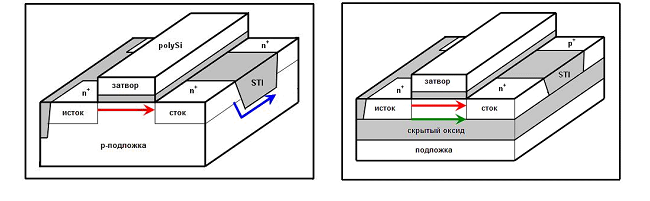

Рисунок 12. Сравнение мест возникновения токов утечки в объемном и КНИ МОП транзисторах. Утечки – основная причина параметрических отказов, вызванных полной дозой излучения. Рисунок наглядно показывает, что КНИ не решает всех проблем с радиационной стойкостью, но принципиальное отсутствие тиристорного эффекта из-за полной изолированности каждого транзистора здорово облегчает разработчикам жизнь, за что многие из них очень любят КНИ.

Так как радиационной стойкостью в России кто только не занимается, упомянуть всех будет решительно невозможно (да и информацию о разработках не раздают на каждом углу), я коротко расскажу о трех компаниях, которые занимаются космическими микросхемами не от случая к случаю, а системно – и, разумеется, занимаются микропроцессорами и микроконтроллерами. Эти компании – «Элвис», «Миландр» и НИИСИ. Я был бы еще рад подробно рассказать про разработки НИИЭТ, но про приемы их защиты от радиации оказалось сложно найти что-то более конкретное, чем общие слова вида «специальные конструктивные и схемотехнические решения, реализованные в микроконтроллере, обеспечивают его устойчивую работу при уровне накопленной дозы не менее 250 Крад и линейной потери энергии (ТЗЧ) до 60 МэВ ∙ см2/мг». Исключение – их LEON, но там все то же самое, что в любом другом LEON-FT – троированные триггеры и помехоустойчивое кодирование в памяти.

АО НПЦ “Элвис”

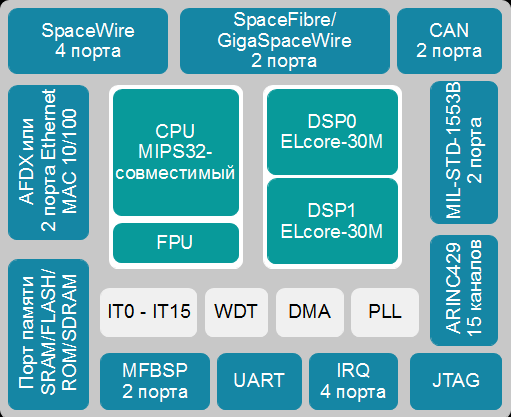

Компания «Элвис» с начала двухтысячных развивает платформу «Мультикор», представляющую собой комбинацию на одном кристалле управляющего RISC-ядра и DSP. Системную работу с обеспечением радиационной стойкости они начали примерно тогда же, совместно с кафедрой электроники МИФИ, сначала на зарубежных технологиях; после появления на «Микроне» собственной 180 нм технологии «Элвис» стали одними из первых внешних клиентов, разработав радстойкую библиотеку логических вентилей и набор IP-блоков для создания систем на кристалле. В описаниях большинства микросхем платформы “Мультиборт» (радстойкая версия “Мультикора”) красуется надпись “микросхема разработана и произведена на территории РФ”. Набор чипов предназначен для построения бортовых сетей передачи данных по стандартам SpaceWire и SpaceFibre и включает процессоры, DSP, память, PLL и коммутаторы.

«Элвис» с самого начала активно участвует в создании и развитии европейского стандарта передачи данных на борту КА SpaceWire (американцы используют свой стандарт – RapidIO), принимая участие в совещаниях международной рабочей группы и являясь главным драйвером внедрения ещё более быстрого стандарта SpaceFibre.

Рисунок 13. Структурная схема процессора 1892ВМ206. Частота работы RISC-ядра – 120 МГц, DSP-ядер – 140 МГц, четыре порта SpaceWire по 300 Мбит/с, два порта SpaceFibre 1.25 Гбит/с и дальше разное полезное по мелочи.

Исполнение на собственной радстойкой библиотеке во всех микросхемах заявлено как основной способ достижения радиационной стойкости. Подробностей о каких-то архитектурных приемах в описаниях на официальном сайте мало, и поиск по публикациям не сделал картину яснее, потому что публикуется “Элвис” мало и в основном на другие темы. Для всех процессоров заявлено кодирование по Хэммингу всей памяти, и в одном из чипов – тройное резервирование регистрового файла и дерева тактовых сигналов. Отнесясь к полноте этой информации со здоровым скепсисом, допустим, что архитектурная защита в “Мультибортах” несколько менее развита, чем в LEON-FT.

АО ПКК “Миландр”

Другой производитель, много занимающийся радстойкими микросхемами – это “Миландр”. Большинство их радстойких чипов так или иначе предназначено для систем бортовой телеметрии – это чипы обработки сигналов с датчиков, аналоговые и цифровые коммутаторы, АЦП, память и, конечно, предмет нашего интереса – три микроконтроллера. Точнее, не три, а два с половиной, потому что 1986ВЕ8Т и 1986ВЕ81Т оба имеют на борту ядра ARM Cortex-M4F, идентичные наборы периферии и различаются только типом памяти программ – ПЗУ в первом случае и SRAM во втором. Предположим, что вариант со SRAM на самом деле нужен для отладки варианта с ПЗУ. 1923ВК014 снабжен более скромным ядром ARM Cortex-M0 и является частью набора микросхем для организации многоканальной системы датчиков, и этот чип – не микроконтроллер в привычном понимании, а специализированный контроллер, заточенный под конкретное применение.

В спецификации на 1986ВЕ8Т и 1986ВЕ81Т (она у них общая) можно найти описание “контроллера обработки событий отказов, сбоев и ошибок”, включающего в себя в том числе функциональность парирования одиночных сбоев, подобную той, которая выше описана на примере процессора ERC32, а также подробное описание функционирования помехоустойчивого кодирования (SECDED код Хэмминга) в разных типах памяти. Никакой открытой информации про, например, тройное резервирование триггеров или дерева тактовых сигналов мне найти не удалось, так что давайте будем считать, что с точки зрения архитектурной сбоеустойчивости 1986ВЕ8Т находится между ERC32 и LEON-FT.

Рисунок 14. Разрез SOI BCD с высоковольтным LDMOS транзистором в изолированном кармане

Технологическая основа для большинства радстойких чипов “Миландра” – библиотеки и набор IP собственной разработки на 180 нм BCD SOI техпроцессе немецкой фабрики XFAB. Эта технология, в отличие от обычной КНИ, имеет толстый приборный слой кремний (порядка микрона) и в большинстве случаев ведет себя, как обычная объемная технология. Наличие скрытого оксида позволяет организовать диэлектрическую изоляцию элементов друг от друга и таким образом гарантировать отсутствие тиристорного эффекта, а то, что он находится на большой глубине, позволяет не беспокоиться по поводу утечек на границе кремния и скрытого диэлектрика, уменьшающих дозовую стойкость обычной КНИ технологии.

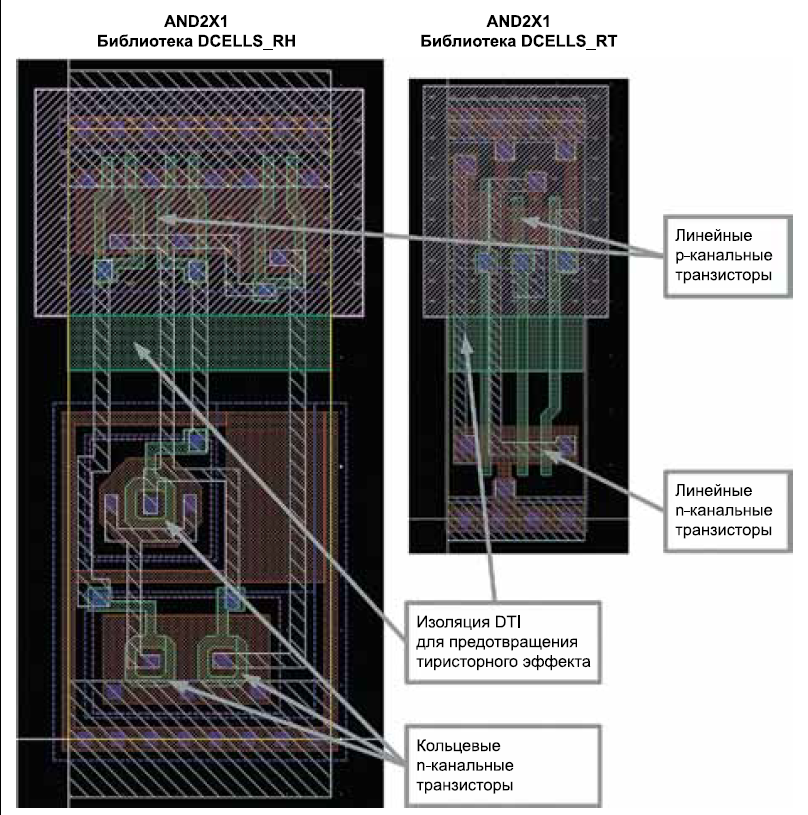

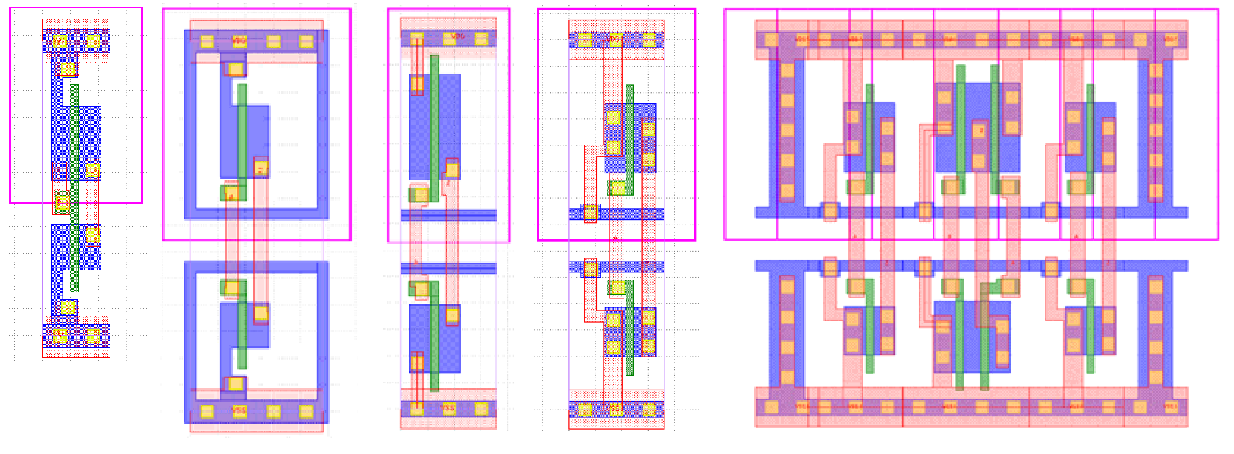

Рисунок 15. Сравнение двух радстойких элементов ИЛИ.

На рисунке показаны два одинаковых логических элемента (двухвходовое ИЛИ) из миландровских библиотек, выполненных с применением разных способов повышения радиационной стойкости. Слева можно видеть кольцевые n-канальные транзисторы, полностью нейтрализующие внутритранзисторную утечку. Однако часто такая радикальная мера избыточна, так как для умеренных доз радиации вполне хватает обычных линейных транзисторов (иногда с небольшими изменениями), и за счёт их применения можно добиться достаточной стойкости при меньшей площади и энергопотреблении – что наглядно и показано на рисунке.

Важная особенность выбранной «Миландром» технологии – наличие в ней транзисторов и других элементов, рассчитанных на работу с высокими напряжениями – до 200 В. Интеграция цифровой логики и силовых приборов на одном кристалле позволяет создавать высокоэффективные DC/DC преобразователи, драйверы ключей, микроконтроллеры с интегрированными драйверами и много других востребованных вещей. Прямо сейчас эти возможности не используются, но когда начнут, «Миландр» получит серьезные конкурентные преимущества над другими разработчиками, потому что прямых аналогов этой технологии в России нет; или 180 нм на напряжения 3.3 В, или высокие напряжения на проектных нормах 1-3 мкм. Работы на тему высоковольтных LDMOS (и даже их радстойкости) публикует последние пару лет НИИСИ, но пока что это только научные публикации, и о серийном производстве речи нет. Ещё весной была новость о том, что проектные нормы 500 нм «для микросхем источников вторичного питания» освоили на Брянском «Кремнии-Л», но никаких подробностей не последовало.

Рисунок 16. Дорожная карта развития радстойких разработок “Миландра” на технологии BCD SOI 180 нм. И да, вы правильно видите в правом нижнем углу слово “ПЛИС”, она у них уже есть и работает.

ФГУ ФНЦ НИИ Системных Исследований РАН

НИИСИ системно исследует вычислительную технику, в том числе и радстойкие микропроцессоры космического применения. Системные исследования, как и положено академическому институту, подразумевают KPI по количеству публикаций, поэтому следить за прогрессом института намного проще, чем за коммерческими компаниями. Нас с вами интересует «космическая» часть линейки «КОМДИВ» (есть ещё «высокопроизводительная» часть).

Архитектура КОМДИВ – это творческая переработка MIPS32, лицензированного НИИСИ в начале девяностых. Изначально институт работал с зарубежными фабриками, а после появления собственного производства начал работать на два фронта, переведя большую часть радстойкой линейки домой. Фабрика НИИСИ расположена в Москве, в Курчатовском институте; она была запущена в 2003 году и представляет собой мелкосерийное опытное производство, размещенное в герметичных кластерах на очень скромной площади. Фактически, усилиями академиков Бетелина, Валиева и Велихова была реализована модная сегодня концепция Minimal Fab, только нормально работающая и на пятнадцать лет раньше японцев (а первым её придумал в Минске В.А. Лабунов в 1983 году). Изначально фабрика работала с проектными нормами 500 нм, позже были освоены нормы 350 и 250 нм, а также технология «кремний на изоляторе», которая и стала основой радстойкой линейки НИИСИ.

Два главных достоинства процессора 1890ВМ1Т (объемная 500 нм технология, 50 МГц) – он работает и он отечественный. Но российские микросхемы настолько суровы, что для низкой орбиты (а именно для бортовых вычислителей новых «цифровых» космических кораблей «Союз-ТМА» и «Прогресс-М») этого хватает, несмотря на полное отсутствие какой-то специальной защиты от радиации. Для нормальной работы 1890ВМ1Т необходим чип-компаньон, отвечающий за работу с внешними интерфейсами (подобно тому, как на трех чипах был сделан ERC32). Для более серьезных условий были разработаны аналоги (серии 5890, 1900 и 1907) на технологии КНИ, позволяющей избавиться от тиристорного эффекта. При этом в чипах 1907 серии интерфейсный контроллер уже находится на том же чипе, что и сам процессор.

Как я уже говорил чуть выше, один из плюсов изучения продукции НИИСИ – обилие публикаций. Для примера возьмём две статьи, вышедшие в IEEE Transactions on Nuclear Science в 2011 и 2013 годах. Первая – M.S. Gorbunov et.al., «Analysis of SOI CMOS Microprocessor’s SEE Sensitivity: Correlation of the Results Obtained by Different Test Methods». В ней описан процессор на КНИ технологии 500 нм с тактовой частотой 33 МГц. Из заявленных архитектурных мер повышения сбоеустойчивости только контроль четности в кэш-памяти, где ошибка вызывает такое же прерывание, как и кэш-промах. Кроме этого, применена специальная топология транзисторов, подавляющая паразитный биполярный эффект и за счет этого увеличивающая порог сбоев (и заодно, по несвязанным причинам, повышающая стойкость к полной дозе излучения). Относительно несложно, но если главная цель – отказоустойчивость, то это ровно то, что нужно. А дальше, когда проблема отказов решена, можно начинать думать о сбоеустойчивости.

Вторая статья – P.N. Osipenko et.al., «Fault-Tolerant SOI Microprocessor for Space Applications». Здесь мы видим уже 350 нм вместо 500, и 50-66 Мгц вместо 33 (производительность 8.9 MFLOPS на 50 МГц). Это все еще не 150 МГц, как у полетевшего примерно тогда же в космос американского RAD750, но прогресс налицо. Еще интереснее – подробно описанная внутренняя структура чипа. Все ядро троировано – не триггеры, как в LEON-FT, а вся комбинационная логика. Это, разумеется, увеличивает в три раза площадь и потребление (1.8 Вт на 66 МГц), но помогает от сбоев не только в запоминающих элементах, но и в комбинационных тоже. Их намного меньше, чем в памяти, потому что они должны совпасть по времени с фронтом тактового сигнала, чтобы повлиять на что-то (и есть еще эффект маскирования, когда сбой не проходит через логику, но это частности), но если вы уже начали делать все как следует, то избавляться надо и от них.

Рисунок 17. Структурная схема процессора K32TMR.

Ядро разбито на несколько некрупных составных частей, на интерфейсах которых проводится голосование (итоги которого логируются). При необходимости, “блоки обеспечения надежности” вызывают прерывания, корректирующие ошибки, требующие внешнего вмешательства (например, повторной загрузки операндов в АЛУ). Сами эти блоки выполнены на транзисторах большего размера, чтобы повысить их помехоустойчивость (в том числе и к помехам, вызванным одиночными частицами). Так как троировать триггеры в уже троированной логике совершенно точно излишне, они стоят по одному, но содержат внутреннюю избыточность по образцу ячейки памяти DICE. Она же взята за основу всех регистровых файлов и кэшей процессора. Регфайлы дополнительно побайтно защищены кодом Хэмминга, кэши – контролем четности. Кроме этого, соседние биты кэшей физически разнесены в пространстве, чтобы минимизировать вероятность двух ошибок в одном байте, а неиспользуемая кэш-память постоянно читается в фоновом режиме, чтобы предотвратить накопление ошибок.

Как видите, в этом процессоре собрано все самое лучшее сразу – на всех уровнях, от библиотечных элементов до архитектуры. Такой подход позволяет добиться действительно выдающихся результатов – сечение насыщения сбоев на порядок ниже, чем у предшественника. На порядок ниже, но за счёт колоссального усложнения чипа. Невольно задаешься вопросом – а точно ли нужно делать все настолько хардкорно? Для многих миссий, особенно не связанных с жизнью людей или критичными к скорости вычислениями (типа посадки на Луну) можно и нужно использовать более простые решения, позволяющие взамен сделать чип быстрее и энергоэффективнее. Для нетроированного чипа 1907ВМ01А4 на проектных нормах 0.25 мкм и потреблении 5 Вт заявлена производительность CPU 89 MIPS (на 100 МГц) и FPU 20 MFLOPS, для троированного 1907ВМ044 на 66 МГц и 9 Вт – 49 MIPS и 14 MFLOPS соответственно. В итоге, судя по большой диаграмме и описаниям с официального сайта, НИИСИ продолжает развивать и троированные ядра, и обычные.

Рисунок 18. Диаграмма о разработке микросхем с официального сайта НИИСИ (выделения мои). В красных овалах – чипы с троированным ядром. Все, что сделано по КНИ технологии – радстойкое.

Из диаграммы видно, что НИИСИ сначала улучшали технологию, а потом на лучших доступных нормах по КНИ развернулись как следует. Самая интересная для нас часть таблицы – верхний левый угол, обещающий развитие троированного радстойкого микропроцессора на технологии 65 нм. Никакой конкретной информации об этом процессоре в интернете, конечно же, нет, но нам на помощь снова приходят публикации, позволяющие посмотреть на исследования радстойкости по 65 нм – а первые статьи по этому поводу датированы аж 2012 годом.

А теперь наконец-то суб-100

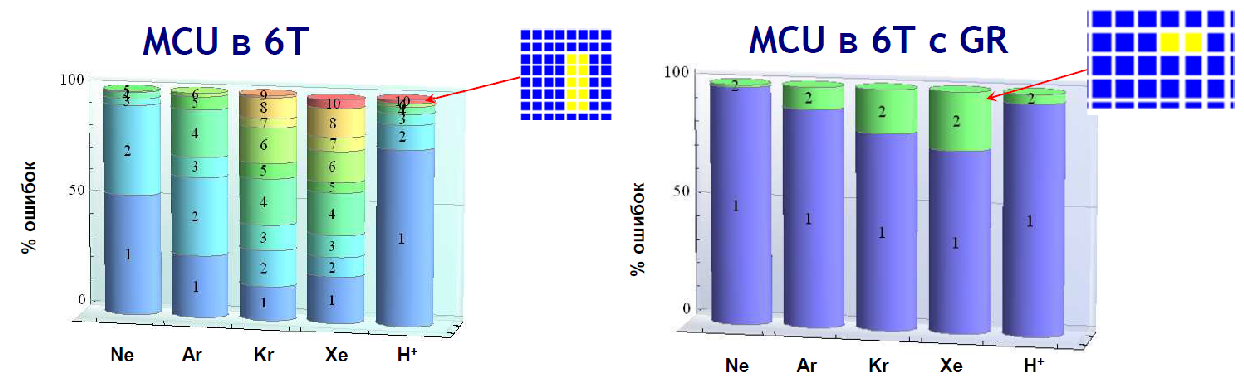

Рисунок 19. Множественные сбои в памяти на примере 65 нм тестового кристалла.

На рисунке показаны результаты попадания одной заряженной частицы разного типа (почти все благородные газы отметились) в массив памяти, выполненный по технологии 65 нм. Слева – обычная память, справа – специально спроектированная радстойкая. Десять сбоев от одного попадания! Не два, не три – десять. Этот эффект вызван тем, что размеры элементов микросхемы постоянно уменьшаются, а вот размер области, из которой собирается избыточный заряд при попадании заряженной частицы остается таким же (около 2-2.5 мкм) – потому что этот размер зависит от диффузии заряда по кристаллу. И вот технология дошла до состояния, когда ячейка памяти стала достаточно маленькой, чтобы любое попадание накрывало сразу много ячеек. То, что это именно диффузия, видно из специфической формы пораженных областей – ровно два столбца, а дальше вправо и влево распространения нет. Отдельно обратите внимание на самый правый столбец – это сбои от протонов, составляющих основную часть солнечной радиации. Они – причина, по которой не стоит просто так запускать за радиационные пояса Земли современные коммерческие чипы (Илон Маск, я сейчас смотрю на тебя и твой полет к Марсу). В правой части рисунка – данные по аналогичной памяти, но радстойкой. Как видите, существенная часть проблем с множественными сбоями (а заодно и со всем остальным) решена – вот только площадь такой ячейки памяти в несколько раз больше обычной. И я даже не буду начинать про то, как собрать на 65 нм ячейку DICE со всеми разнесенными в пространстве транзисторами, попутно перемешав две или четыре таких ячейки для экономии места и не запутавшись в получившейся многоуровневой лапше из металлизации. Впрочем, среди публикаций НИИСИ есть и такие работы.

Рисунок 20. Сравнение топологии обычной 6Т ячейки памяти (справа вверху) и радстойкой версии из библиотеки DARE65 (IMEC, Бельгия). Ярко-синие – затворы, коричневый – активный кремний.

С троированными триггерами тоже весело – для того, чтобы два запоминающих элемента не сбились от одной и той же частицы, их надо разнести на те самые 2-2.5 микрона. В 180 или 350 нм это несложно, а вот по нормам 65 нм площадь троированного триггера получается в двенадцать раз больше, чем у обычного (и большая часть этой площади – пустая). В итоге с точки зрения и потребления, и площади, и простоты дизайна в САПР схема со сквозным троированием, выполненная на полностью стандартных элементах, разнесенных достаточно далеко друг от друга, получается выгоднее, чем применение готовых троированных триггеров и других базовых элементов с внутренней избыточностью.

Рисунок 21. Тройное модульное резервирование и двойное модульное резервирование с самоголосованием. Из статьи J.Teufel, “Self-Voting Dual-Modular-Redundancy Circuits for

Single-Event-Transient Mitigation”, IEEE Transactions on Nuclear Science, 2008 (Sandia Labs все еще с нами, точнее все еще с ними)

Схема на рисунке датирована аж 2008 годом и показывает, что в менее публичных продуктах, чем RAD750 (а основная сфера деятельности Sandia Labs – американская военная ядерная программа) наши заклятые друзья тоже используют много разного интересного. В частности, в упомянутой выше статье и в некотором количестве других недавних публикаций подробно разбирается вопрос того, как в разных по важности частях чипа применять совместно тройное и двойное модульное резервирование. И, кстати, если у элемента голосования достаточно большая задержка, то он в схеме с двойным резервированием будет фильтровать одиночные сбои в логике, и результат будет настолько же стойким, как и тройное резервирование.

А теперь давайте посмотрим, как выглядят библиотечные элементы на технологии 65 нм. Цитирую опять же работу из НИИСИ – Ю.Б. Рогаткин и др., “Разработка библиотеки радиационно-стойких элементов по 65 нм КМОП технологии”, Труды НИИСИ РАН, 2018 год. Так как забота о сбоеустойчивости практически полностью перенесена на другие уровни разработки – архитектуру и автоматический синтез топологии с учетом ограничений на расположение элементов – то основными задачами разработчиков библиотек элементов снова стали защита от полной поглощенной дозы и тиристорного эффекта.

Рисунок 22. Логические ячейки, выполненные по технологии 65 нм.

Самый левый элемент на рисунке – обычный библиотечный инвертор.

Второй элемент – его радстойкая версия, снабженная охранными кольцами, предотвращающими тиристорный эффект. Важно, что у кольца контакты к металлу только с одной стороны, и надо иметь в виду сопротивление слоя кремния, которое может быть достаточно большим, чтобы повлиять на эффективность этого решения.

Третий – все тот же инвертор, у которого для экономии площади боковые стороны охранного кольца отрезаны.

Четвертый – он же, но с контактами к внешней части охранных колец, чтобы хорошо контролировать их сопротивление и не заботиться о том, как именно они собраны в блоки.

Пятый – блок из двух инверторов и элемента 2ИНЕ с показанными закрывающими частями охранных колец.

Что касается полной дозы излучения, то здесь на суб-100 нм нормах все даже проще и понятнее, чем на старых технологиях. Токи утечки в них уже есть безо всякой радиации, на них и так все закладываются, осталось только ввести дополнительную поправку на то, что они будут расти еще. В типичных технологиях такого уровня обычно предлагается три варианта транзисторов – с низкими пороговым напряжением (быстрые, но с большими утечками), со средним пороговыми напряжением и с высоким пороговым напряжением (медленные, но с маленькими утечками), и пользователь может комбинировать их при необходимости. Стандартные библиотеки обычно тоже сделаны в трех вариантах, а при проектировании радстойкой надо подобрать компромисс между скоростью и утечками, учитывая то, соединены транзисторы последовательно или параллельно.

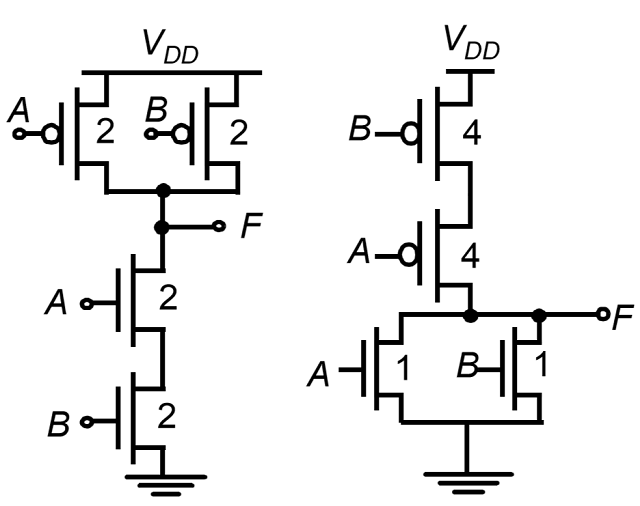

Рисунок 23. Схемы логических элементов 2И-НЕ и 2ИЛИ-НЕ.

В элементе 2ИЛИ-НЕ n-канальные транзисторы соединены параллельно, что удваивает утечку, а значит имеет смысл применить в этом месте транзисторы с более высоким пороговым напряжением. А в 2И-НЕ они соединены последовательно, и там можно оставить обычный порог транзисторов. И такие рассуждения (желательно подкрепленные данными измерений) нужно применить ко всем нескольким сотням элементов в библиотеке, а потом еще подумать о том, что делать с запоминающими элементами, чтобы они меньше сбивались, и чтобы утечки через аналоговые ключи, обычно применяемых в современных триггерах, все не сломали, и так далее и тому подобное.

По состоянию на сегодняшний день в НИИСИ существует полноценная платформа для разработки на проектных нормах 65 нм, включающая библиотеки, IP-блоки, компиляторы памяти, скоростные интерфейсы и т.д. Важно также то, что эта платформа лицензируется другим российским компаниям, что позволяет ускорить преодоление отставания от американцев, а европейцев практически нагнать. Если бы еще фабрика была не TSMC, а своя, как в Америке и Европе… Но это уже другая история, которая разворачивается на наших глазах. 65 нм техпроцесс “Микрона” после 2014 года застыл в статусе “проходит квалификацию и освоение в производстве”, и новостей о нем уже довольно давно нет; зато в последние несколько месяцев было достаточно новостей о долгосрочных планах создать в России производство по нормам 28 нм. Когда эти планы будут реализованы и будут ли – большой вопрос.

Подытоживая эту часть, отметим, как с уменьшением проектных норм ещё раз изменились задачи, стоящие перед разработчиками. Глубоко субмикронные технологии имеют стойкость к полной дозе радиации, достаточную для большинства применений, и позволяют организовать защиту от тиристорного эффекта и одиночных/множественных сбоев на этапе разработки чипа, без модификации исходного техпроцесса. Это помогает удешевить производство и ускорить освоение новых технологий. Главные тормоза прогресса – экономические: разработка и всестороннее изучение как тестовых, так и «боевых» чипов серьезно дорожают с каждым новым поколением технологии, а мизерные тиражи космических микросхем не позволяют нормально компенсировать эти затраты. Поэтому разработчики стремятся максимально использовать возможности каждой применяемой технологии и пользоваться ей как можно дольше, переходя дальше только тогда, когда это абсолютно необходимо и создавая платформы для разработки и позволяющие создавать широкую номенклатуру микросхем. Российские разработчики сегодня совсем немного отстают от западных коллег, и причины этого отставания не научные или инженерные, а организационные и экономические.

Вынужденно короткий разбор всех остальных

Япония

Японское космическое агентство JAXA умеренно участвует в международной активности, и большинство своих космических исследований японцы проводят самостоятельно. Миссии впечатляют амбициозностью и потрясающими историями про успешное преодоление возникающих на орбите сложности. Если бы Мэтт Дэймон мог сыграть космический зонд, то мы бы уже видели в прокате фильмы и про «Хаябусу» (японцы, кстати, уже сняли их аж три штуки), и про «Акатсуки». Микропроцессоры для космоса, как и все остальное, у японцев свои, на собственных архитектурах, и даже проектные нормы производства у них не такие, как у остального мира (300 и 200 нм например). Я бы с огромным удовольствием написал об этом подробно, но информации мало, а информации на неяпонском языке почти нет, поэтому придется ограничиться кратким обзором.

Рисунок 24. Типовой источник информации по японским радстойким процессорам.

Основные приборные поставщики JAXA – Hitachi, NEC и MHI (Mitsubishi Heavy Industries). В восьмидесятых японская индустрия была увлечена проектом TRON, предлагавшем сквозной дизайн сетевой инфраструктуры. Операционной системой реального времени TRON японцы пользуются в промышленности и в космосе до сих пор, а вот архитектуру микропроцессоров TRON довольно быстро бросили (хотя радстойкие чипы по ней были сделаны и, весьма вероятно, летали) в пользу MIPS64 (в случае с NEC) и другой японской 32-битной архитектуры SuperH (H – это Hitachi; ее версию SH2 можно встретить в японских автомобилях, а SH4 – в приставке Sega Dreamcast и автомобильной продукции компаний Hitachi и Renesas).

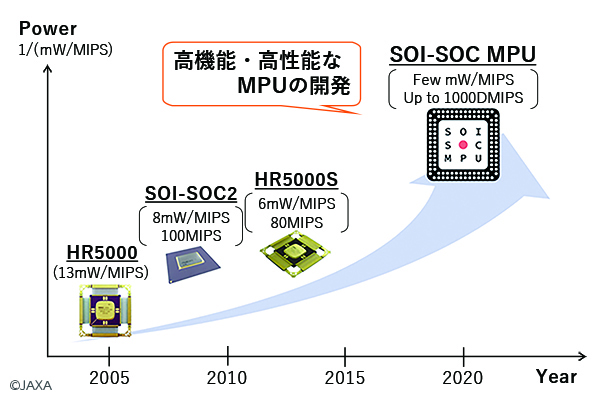

Рисунок 25. Японские космические микропроцессоры. HR5000 – MIPS64, SOI-SOC – SH4.

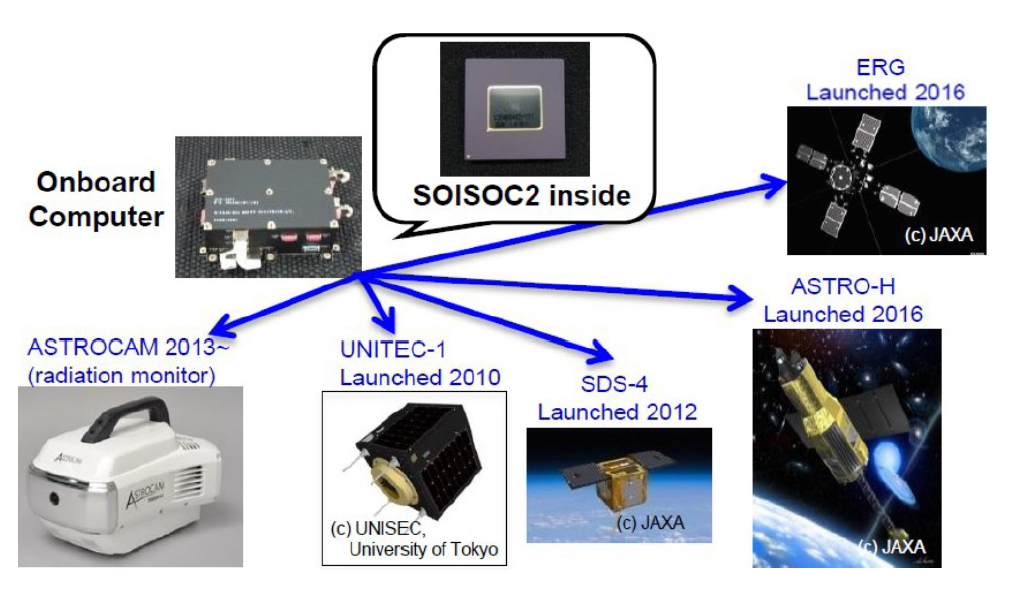

Рисунок 26. Иллюстрация применений SOI-SOC2.

“SOI” в SOI-SOC разумеется, означает “кремний на изоляторе”. Технологический уровень SOI-SOC3 – 200 нм, у находящегося в разработке следующего поколения будет меньше. Также небольшая, но важная цитата от JAXA: “There is a big problem of soft errors in consumer/industrial processors due to atmospheric neutrons on the ground level. SOI-SOC MPU will be delivered as high-reliability parts to users of those processors”. Проблема атмосферных нейтронов в первую очередь касается авиации, но это уже другая история. На этом с японцами все, переходим к их соседям.

Китай

Китайская космическая программа – самая быстроразвивающаяся и одна из самых закрытых, информации о японских процессорах по сравнению с китайскими просто море. Сказать что-то конкретное сложно – кроме того, что начинали китайцы с послойного копирования всего подряд, и что в 2014 году у них нашлось для России множество позиций, попавших под санкции. В последнее время, впрочем, и в китайскую космонавтику, и в китайскую микроэлектронику вкладывается много денег, и самые новые аппараты летают на разработанных Китайской Академией наук MIPS-совместимых процессорах (ничего не напоминает?) Loongson. На гражданских Loongson строятся ПК, планшеты и даже суперкомпьютер; этот процесс значительно ускорился после начала торговой войны США и Китая.

Израиль

Космическое агентство Израиля было основано в 1981 году, первый собственный спутник был запущен с территории Израиля в 1988. Сейчас Израиль разрабатывает и запускает (самостоятельно и с чужих космодромов) несколько семейств гражданских научных и военных аппаратов. Сведения об их начинке мне найти не удалось, но рискну предположить, что по крайней мере первые разведывательные аппараты, разработанные одним из основных израильских авиационных подрядчиков, летали на чипах архитектуры 1750А. В современных гражданских разработках израильские компании много сотрудничают с европейскими коллегами, так что логично предположить использование LEON-ов. Подтверждение тому – то, что частный спутник «Берешит” в прошлом году летел на GR712, разработанном и произведенном в Израиле варианте LEON.

Индия

В Индии нет своего производства микросхем, только опытная фабрика местной академии наук (ничего не напоминает?) с нормами 180 нм. Какие-то исследования по радстойкости индусы ведут, но ничего важного от них не слышно. По имеющимся отрывочным сведениями из разных источников, для своих спутников они применяли/применяют ERC32 и варианты процессоров LEON, а великолепная марсианская миссия “Мангальян” и вовсе управлялась процессорами архитектуры Mil-Std-1750А (опять же европейскими).

Бразилия

Бразильская микроэлектроника – почти как бразильская космическая программа: вы о ней ничего не знаете, но она существует. В частности, бразильцы – сильные специалисты по части исправления одиночных сбоев на обычном железе при помощи программных методов (например, выполняя часть команд по несколько раз и сверяя результаты) и по сбоеустойчивости FPGA. Профильные университетские группы активно участвуют в международных научных конференциях и делают совместные проекты с европейскими и американскими коллегами.

На этом, кажется, все. Остальные страны не ведут самостоятельных разработок космических микропроцессоров или систем на их основе, закупая ключевые компоненты, блоки или спутники в сборе на стороне, как например Пакистан, развивающий собственное спутникостроение в тесной кооперации с китайцами. Ну и понятно, что начинка иранских и северокорейских аппаратов известна только их создателям и, если повезло, некоторым разведкам. Мы не разведка, поэтому давайте переходить к следующей части.

Ближайшее будущее – на примере всех вместе

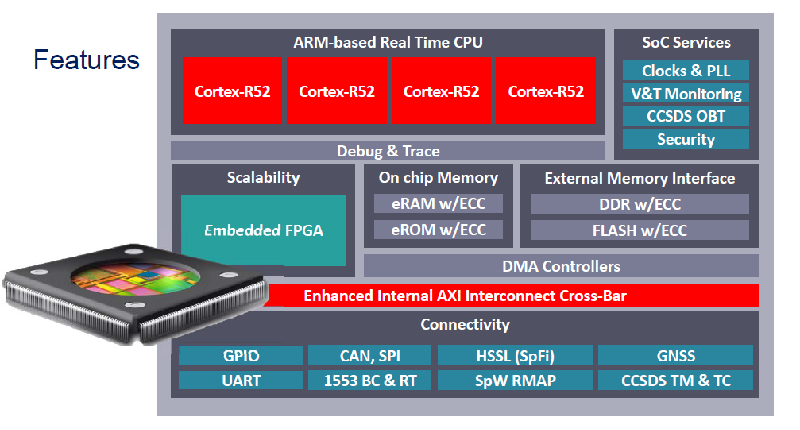

Технологический уровень новейших космических микропроцессоров – это 45 нм для США (RAD5500), 65 нм для Европы (GR740) и 65 нм для России (уже в этом году обещают что-то выпустить). При этом в первых двух случаях мы можем наблюдать смену поколений – в США следующее поколение космических процессоров (HPSC) будет делать не нынешний монополист BAE Systems на архитектуре PowerPC, а Boeing на ARM (по проектным нормам 32 нм на технологии КНИ), а в Европе параллельно с выходом очередного SPARC LEON ведется проект многоядерного процессора DAHLIA с архитектурой ARM на проектных нормах 28 нм (тоже КНИ). Параллельно Европейское космическое агентство в своем обычном желании не зависеть от чужих лицензий начало разработки на новой архитектуре RISC-V, стремительно набирающей обороты в коммерческом секторе и обрастающей софтверной экосистемой. Первые прототипы TMR-модифицированных чипов RISC-V уже продемонстрированы в 2018 году коллаборацией Antmicro и Thales. Несмотря на всю популярность LEON (как говорится, в узких кругах), в сторону SPARC давно уже были вопросы о софтовой поддержке, и конкуренты спешат этим воспользоваться. Особенно спешат конкуренты с ARM, потому что фактически бесплатный доступ к огромному количеству индустриального и коммерческого прикладного ПО – это очень важный козырь в разговорах с разработчиками космических аппаратов, важность которого стремительно растет по сравнению с желанием иметь обратную совместимость со старыми проектами.

Кроме микропроцессоров и DSP, где скорость – очевидный приоритет, есть спрос и на микроконтроллеры. Такие чипы есть на большинстве озвученных архитектур – европейский GR716 (SPARC/LEON), американские RAD EMC (PowerPC), ARM от разных производителей (Vorago, Microchip, „Миландр“, „Ангстрем“), радстойкие версии MSP430 от Texas Instruments, MCS-96 и MCS-51 от НИИЭТ и так далее и тому подобное. Микроконтроллеры обычно защищают попроще, чем их “большие” собратья, с упором на отсутствие отказов (тиристорного эффекта) и с минимальной коррекцией покупных ядер (или с никакой коррекцией и синтезом с использованием троированных триггеров и специальных библиотек элементов). Возвращаясь к процессорам, давайте посмотрим на то, какие суб-100 нм платформы разработки существуют или объявлены прямо сейчас.

Рисунок 27. Суб-100 нм платформы разработки радстойких интегральных микросхем.

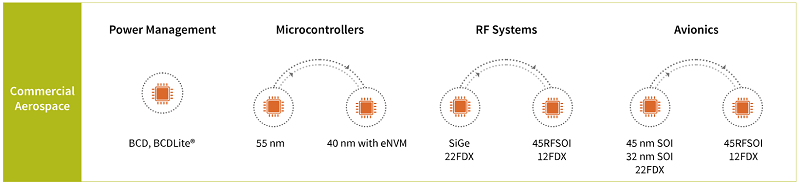

65 нм для разработчиков Европы и России – это уже “сегодня”, а американцы вообще со 150 проскочили сразу на 45 нм. Скорее всего, в ближайшие лет десять основными будут именно эти технологии, а более тонкие нормы, уже показанные на этой диаграмме, перейдут с ранних на поздние стадии разработки. Впрочем, то, что показано на рисунке – это только большие публичные коллаборации, на самом деле ничего (кроме времени и денег) не мешает разрабатывать радстойкие чипы на других техпроцессах без лишнего шума. Например, GlobalFoundries предлагают для создания аэрокосмических чипов целую линейку технологий на разные вкусы и бюджеты. Именно на их мощностях производятся новейшие RAD5545, на них же будут производиться и HPSC; это неудивительно, потому что фабрики GloFo имеют сертификацию Trusted Foundry еще со времен, когда они принадлежали IBM. И вряд ли все заявленные процессы стоят без американских клиентов.

Рисунок 28. Предложения GlobalFoundries для Aerospace индустрии.

На мощностях GlobalFoundries, правда не американских, а немецких (в Дрездене) планируют производить свои будущие радстойкие чипы IMEC (а значит, вся Европа за вычетом STM) и „Миландр“.

Рисунок 29. Дорожная карта „Миландра“ по освоению радстойких чипов на 22 нм технологии. Как видите, планов очень много, включая большие FPGA и быстрые АЦП для Software Defined Radio (SDR). Первый тестовый чип уже произведен, так что с нетерпением ждём хороших новостей.

Что такое FDSOI? FD – это Fully Depleted, полностью обедненный; тонкий активный слой кремния между подзатворным оксидом и скрытым оксидом полностью обедняется, и канал транзистора занимает его целиком. Это позволяет окончательно ликвидировать паразитные ёмкости стока и истока, а также убрать путь утечки по глубине кремния, характерный для аналогичных объемных технологий, и уменьшить статическое энергопотребление. Кроме того, вместо использования нескольких типов транзисторов, как в объемной технологии, в FDSOI можно локально подавать отрицательное или положительное напряжение под скрытый оксид, таким образом изменяя порог транзистора (а вместе с ним скорость и энергопотребление) – в зависимости от того, находится чип в активном или в спящем режиме. Все вместе это делает FDSOI крайне привлекательным, например, для интернета вещей. Или для малопотребляющих космических схем, благо КНИ технология автоматом избавляет разработчика от головной боли с катастрофическими отказами из-за тиристорного эффекта.

Рисунок 30. Разрезы объемного и FDSOI транзисторов.

Главный недостаток FDSOI с точки зрения радиационной стойкости – дополнительный путь утечки по границе канала и скрытого оксида. Накапливающийся в скрытом оксиде заряд играет роль приложенного к скрытому оксиду положительного напряжения, и вместо управления поведением транзисторов через нижний затвор приходится перекомпенсировать влияние радиации. А чтобы это сделать, надо подавать большое отрицательное напряжение – которое усилит процесс накопления заряда в скрытом оксиде и ухудшит дозовую стойкость. В общем, получается заколдованный круг, выход из которого может оказаться нетривиальным. Желающих его поискать, правда, достаточно много, так что можно запасаться попкорном. Первый попкорн пригодится уже совсем скоро – европейский проект DAHLIA почти завершен.

Рисунок 31. Структурная схема DAHLIA. 28 нм FDSOI, четыре ядра ARM-Cortex R52 (обещают 4000 DMIPS на 600 МГц), заточенных под real-time приложения с развитым разделением полномочий, память на борту, большинство популярных интерфейсоа и даже встроенная FPGA на 500 тысяч LUT, чтобы одним чипом точно покрыть потребности всех пользователей на много лет вперед.

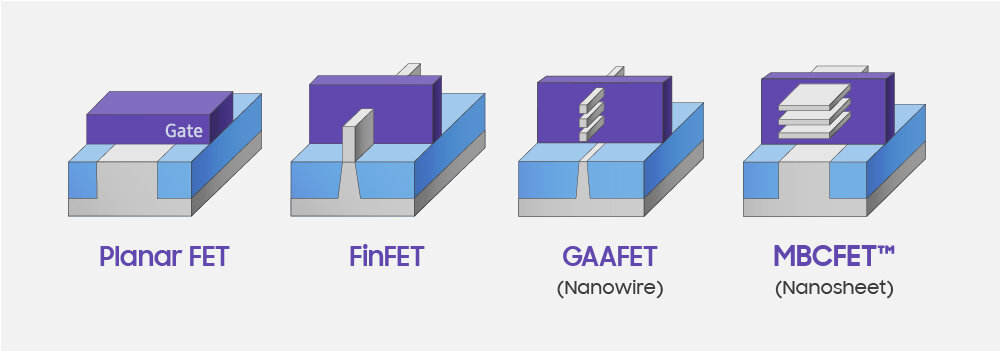

Объемная технология тем временем не собирается сдаваться. Она может предложить разработчикам отсутствие „лишнего“ маршрута утечки и, в долгосрочной перспективе, меньшие проектные нормы. Более того, в FinFET транзисторах затвор начинает охватывать канал все плотнее, а изолирующий оксид отодвигается от сильного электрического поля, что тоже должно положительно повлиять на стойкость к полной дозе излучения. В IMEC уже начинают разработку радстойких библиотек по 16 нм, а коммерческая индустрия продолжает осваивать новые технологии.

Рисунок 32. Различные поколения МОП-транзисторов.

В долгосрочной перспективе GAA (Gate All Around) от Samsung обещают быть устойчивыми к полной дозе радиации, окончательно избавив разработчиков от проблем с ней – в них просто не существует никакого побочного пути из истока в сток, мимо основного канала и основного затвора, а подзатворный диэлектрик настолько тонкий, что сдвиг порогового напряжения будет пренебрежимо мал даже на очень больших дозах. Но, конечно же, наверняка будут какие-то новые сложности – не только с одиночными сбоями, но и, например, с эффектами смещения, уже вовсю беспокоящими проектировщиков HEMT транзисторов на нитриде галлия. В приборах из сложных полупроводников квантовые и наноразмерные эффекты не в новинку, и знания о них совсем скоро потребуются и разработчикам на кремнии, так что на ближайшие много лет работы по обеспечению радиационной стойкости микросхем для космоса будет хватать. А ведь есть ещё адронные коллайдеры, атомная и термоядерная энергетика; прогресс неумолим и он не собирается останавливаться – зато на этой позитивной ноте собираюсь остановиться я. Спасибо, что прочитали до конца, надеюсь, было интересно.