Когда я видел на Хабре упоминание о ПЛИС Lattice, у меня всегда возникал простой вопрос: «А зачем ещё одна ПЛИС?». Вроде всю жизнь хватало пары базовых. Но полгода назад случилось то, что сняло этот вопрос для меня. Пришёл Заказчик и сказал: «Мы делаем проект на ECP5». Против требований Заказчика не попрёшь!

А пока я осваивал работу с этим железом и пытался понять, как обосновать необходимость попробовать то же самое для остальных, мой знакомый, ныне живущий в Штатах, обрадовал новостью, что у его любимого поставщика подходит к концу запас десятых Циклонов и шестых Спартанов. В целом, через три года будет построен новый завод Intel, но что именно там будут производить, он не в курсе. И три года продержаться в любом случае, будет нужно. Короче, сейчас надо иметь возможность быстро мигрировать с одной ПЛИС на другую.

Итого, вчера делать ознакомительную статью про Lattice было рано, завтра – может быть поздно.

Сегодня я расскажу, где купить более-менее дешёвые платы для опытов, как быстро освоить Open Source среду разработки и какие готовые проекты осмотреть в первую очередь.

1 Ограничения в возможностях

Давайте начну с не самого приятного. Может так получиться, что кто-то даже бросит читать на этом разделе, но так будет лучше, чем он сначала загорится идеей, а потом – разочаруется в ней.

1.1 Ограничение для семейства ICE40

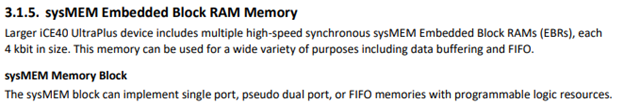

Первая ПЛИС Lattice, с которой мне довелось поработать, относилась к семейству ICE40. И вот, что первое бросилось в глаза из фирменной документации:

Память может использоваться в однопортовом и псевдодвухпортовом режиме. То есть, один порт на запись, второй – на чтение. Реальная двухпортовость недоступна. Ну, и преобразование ширины шины тоже весьма ограниченное.

Я даже сильно расстроился, но к счастью, работы с ICE40 были быстро свёрнуты, а у семейства ECP5 с двухпортовостью всё в порядке. По крайней мере, судя по описанию. Жаль, но вторая проблема характерна для обоих семейств.

1.2 Ограничение как для ICE40, так и для ECP5

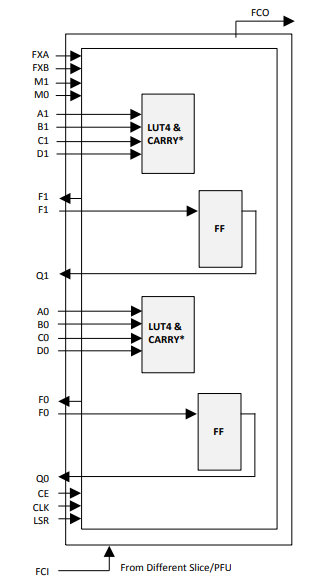

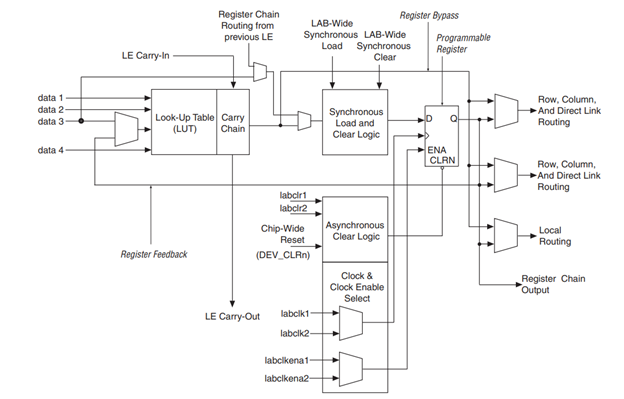

Давайте взглянем на типовую ячейку ПЛИС Lattice семейства ECP5.

А теперь – на её аналог в довольно древней ПЛИС Altera Cyclone IV:

Обратите внимание, что Альтеровская система, как паук, обросла линиями для связи соседних ячеек без выхода в область глобальной трассировки. Многобитовые функции могут быть реализованы как макрофункции из блоков, расположенных рядом друг с другом, поэтому связи идут через прямые межблочные соединения. А у Lattice, по крайней мере из логов, которые я вижу на практике, всё идёт через глобальные трассировочные ресурсы. Как следствие, можно получить такой отчёт о задержках в критической цепи:

Как не вспомнить знаменитое: «За морем телушка – полушка, да рубль перевоз»?

Итого: одни и те же исходники для Альтеры и для Латтиса дадут сильно разное значение FMax (максимальной допустимой тактовой частоты) для построенной системы. И разница будет всегда в пользу Альтеры.

А в остальном – ну ПЛИС, как ПЛИС. Так что кто не сильно напугался, идём дальше.

2 С чем поиграть

Если искать макетные платы по семейству ECP5, будут найдены довольно дорогие варианты. Вот, например, цена на типовую модель Orange Crab в магазине «Чип и дип»:

В других местах цена будет ничуть не лучше. Тушим свет? Вовсе нет! Ищем на Али по запросу colorlight 5a 75b

Я покупал летом: цена в сумме с доставкой вообще была чуть ниже тысячи рублей. Но и сейчас она не самая страшная:

За эти деньги вы получите плату с не самой слабой ПЛИС, тактовым генератором, стабилизатором, двумя микросхемами SDRAM, в сумме обеспечивающими 32-битную шину данных, и двумя гигабитными Ethernet каналами. Неплохо, да?

Правда, дальше всё чуть хуже. Эта плата должна управлять светодиодными панелями. Поэтому у неё имеется очень много выходов. Но все они сделаны 5-вольтовыми. Для этого, на плате стоит очень много шинников. Кто привык к советской системе – АП6, для остальных – 245. И у этих шинных формирователей направление намертво зажато на выход. Ну, потому что если переключить их на вход – они своими пятью вольтами сожгут ПЛИС.

Что можно сделать? В нашем случае, мы ничего не делали. У нас стояла задача освоить работу с гигабитной сетью. Так что мы просто пользовались имеющимися PHY. А так – в сети я нашёл три решения.

3 Как заменить выходы на двунаправленные варианты

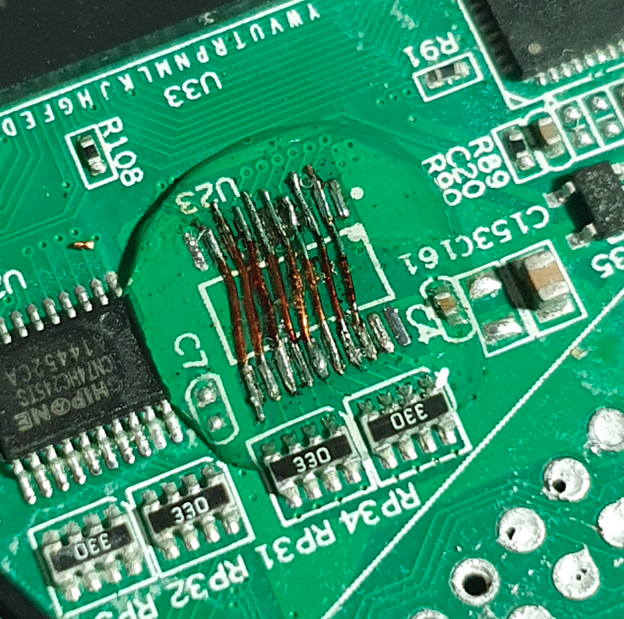

Первый вариант: народ просто снимает шинники и ставит перемычки. Вот такая красота показана на странице Hacking a ESP32 into FPGA Board.

Всё бы ничего, но там шаг выводов 0.5 мм. Так что паять придётся долго и мучительно.

Второй вариант: замена шинного формирователя на двунаправленный преобразователь уровня. Она описана тут.

Я поглядел на Али Экспресс. В чистом виде SN74CBT3245APW практически отсутствуют. Их аналог, CU245A, представлен шире, но купить замену для всех чипов, по цене выйдет, как вся плата… Рентабельность низковата. Другое дело, что можно заменить только часть шинников, оставив остальные линии чисто выходными… Так или иначе, у меня пока такой задачи не стояло, поэтому я просто запомнил идею, а никаких доработок не производил.

Наконец, третий вариант: взять чуть иной вариант платы, но уже и по менее привлекательной цене (там в сумме выйдет около трёх тысяч рублей).

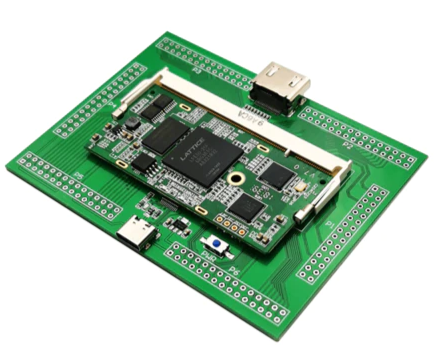

Везде в основе будет лежать модуль с разъёмом So-DIMM, но в одном случае его выводы могут быть выведены напрямую:

Ура? Нет, не ура. Видите две квадратных микросхемы справа на самом модуле? Это те самые гигабитные PHY. А трансформаторной развязки и разъёмов для них нигде нет. Ни на модуле, ни на материнке. Крупный разъём на материнке – это не Ethernet, а HDMI.

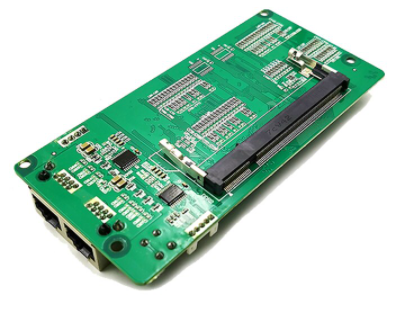

На втором варианте материнок Ethernet-обвязка есть…

Но зато с удивительными разъёмами и необходимостью настраивать работу с шинниками через нулевые резисторы для каждого бита. В общем, куда ни кинь – всюду клин. Правда, если вы будете делать свой промышленный проект – вы же «материнку» сможете развести свою, какую надо. А для опытов – взять вариант за тысячу рублей, чтобы не тратиться.

4 Версии платы за тысячу рублей

Ещё не испугались? Тогда продолжаю рассказывать про весёлые моменты… Плата Colorlight 5A-75B может приехать версии 6.1, 7.0 или 8.0. Причём я заказал себе одну на пробу – приехала седьмой версии. Я решил заказать ещё… Заказал строго там же. Приехало две платы восьмой версии. Так что угадать, что приедет – нельзя.

Все ссылки по проектам, которые я дам ниже – рассчитаны на версию 7.0. Цоколёвка ПЛИС у всех трёх версий не совпадает в принципе. Поэтому, если вам приедет какая-то другая версия платы, не забудьте в типовых проектах поменять назначение выводов.

5 Схема платы

Схемы платы в чистом виде в открытом доступе нет. Но любители произвели исследования и выложили результаты. Я обычно смотрю справочники тут: chubby75/5a-75b at master · q3k/chubby75 (github.com). Здесь имеются цоколёвки включения ПЛИС для всех трёх версий. Ну, и фотографии, а также документация на многие микросхемы, установленные на платах.

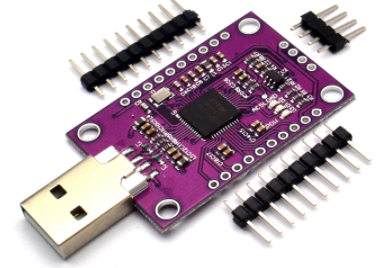

6 JTAG-адаптер

Есть разные способы заливки «прошивки» в ПЛИС. Лично я использую OpenOCD и плату на базе FT232H. Не 2232H, а просто 232H. То есть, одна двойка в маркировке (она дешевле), но обязательное наличие буквы «H».

Файл конфигурации для OpenOCD, в итоге, я нашаманил вот такой:

adapter driver ftdi

ftdi vid_pid 0x0403 0x6014

ftdi layout_init 0xfff8 0xfffb

ftdi layout_signal nTRST -data 0x0100 -oe 0x0100

ftdi layout_signal nSRST -data 0x0200 -oe 0x0200

adapter speed 1000

jtag newtap lfe5u25 tap -expected-id 0x41111043 -irlen 8 -irmask 0xFF -ircapture 0x05

init

scan_chain

svf -tap lfe5u25.tap -quiet -progress blink.svf

shutdown

Таблица соединения:

|

Цепь JTAG |

Цепь FT232H |

|

TCK |

AD0 |

|

TDI |

AD1 |

|

TDO |

AD2 |

|

TMS |

AD3 |

7 Среда разработки

Вообще, Lattice распространяет свою среду разработки Diamond. Но что мы делаем, когда надо разработать что-то под ПЛИС Altera/Intel? Скачиваем бесплатную версию Квартуса, устанавливаем, запускаем, работаем. Так? Здесь всё сложнее. Сначала надо подтвердить, что вы не являетесь сотрудником компаний из какого-то санкционного списка. После чего, вам дадут лицензию… На год!!! Здорово, да?

К счастью, есть альтернативное решение. Для этих ПЛИС есть среда разработки с открытым исходным кодом. Синтезатор называется Yosys, трассировщик – NextPNR. Для Линукса, их можно собрать из исходников, можно скачать готовый набор. Чуть ниже расскажу, откуда. Но сначала упомяну Windows. Дело в том, что я – очень стар. Я начинал с ОС RT-11 ЭВМ семейства «Электроника». Само собой, потом был ДОС и Windows, начиная с 3.1. Поэтому я уже испорчен. И долгая работа с Линуксом, доставляет мне некоторые неудобства. Это уже не лечится.

Но оказывается, и Yosys, и NextPNR могут быть собраны, как обычные Windows-приложения. Даже не в режиме эмуляции, а как полноценные EXE-шники. Другое дело, что сделать это удалось только при помощи серпа, молота и какой-то матери. В сумме, я просидел почти рабочую неделю, чтобы всё собралось и заработало. Но оно работает! Работает!!! РАБОТАЕТ!!! Если вдруг будет спрос, я могу формализовать правила сборки. Просто повторять тот подвиг чисто ради графоманства – слишком геройская задача. Не для меня.

Теперь обещанная ссылка, откуда можно взять готовый набор инструментов Yosys/NextPNR для Линукса (ссылку предоставил Заказчик):

GitHub — YosysHQ/fpga-toolchain: Multi-platform nightly builds of open source FPGA tools

Ну, а там наши Верилоговские проекты обычно собираются через makefile. Чтобы не осваивать процесс с нуля, лучше найти готовые примеры. Вот давайте рассмотрим парочку, позволяющих ощупать работу с этими ПЛИС с разных сторон.

8 Пара готовых примеров

8.1 blink

Функционально данный пример просто мигает светодиодом. Но организационно он позволяет убедиться, что среда разработки установлена верно, JTAG-адаптер функционирует, и плата исправна. Плюс, его makefile и файл назначения выводов ПЛИС могут послужить основой для развития, чтобы получить в итоге собственный большой проект.

Подобных проектов много. Я буду говорить о скачанном отсюда: kholia/Colorlight-5A-75B: Notes for Colorlight-5A-75B. (github.com)

Единственное, на что стоит обратить внимание в этом проекте: внутри makefile есть ошибка. Вот имеется строка:

TOP=blink

Логично же, что модуль верхнего уровня – blink, правда? И в этом проекте оно так и будет. Но когда я переписал всё так, что в проекте стало много файлов (подтянул Open Source проект verilog-ethernet), компилятор долго выдавал какие-то непонятные ошибки. Только через некоторое время по логам я понял, что он решил, что модуль верхнего уровня лежит в каком-то файле, реально находящимся глубоко в иерархии. Оказалось, что переменная TOP назначается, но не используется. Надо добавить её в строку вызова синтезатора:

$(TARGET).json: $(OBJS)

yosys -p «synth_ecp5 -top $(TOP) -json $@» $(OBJS)

Обратите внимание также на файл blink.lpf. В нём содержится описание цоколёвки выводов, а также требуемых частот для тактовых сигналов.

Если у вас плата не версии 7.0, не забудьте заменить номера выводов, согласно описанию на свою версию.

8.2 Шина Wishbone с управлением через Ethernet

Этот проект позволит нам ни много ни мало быстро проверить работоспособность одного канала Ethernet на плате, а также покажет, как более детально настраивать частоты внутренних тактовых сигналов проекта, пользоваться DDR линиями… Да и вообще, очень полезный проект-справочник.

Скачать его можно тут: enjoy-digital/colorlite: Take control of your Colorlight FPGA board with LiteX/LiteEth 🙂 (github.com)

Кто в теме, тот уже понял, что значит слово LiteX. Для остальных, кратко поясню. Это такая система, которая позволяет писать «прошивки» для ПЛИС на языке Python. Сам я это дело не одобряю, но нам этот язык сейчас ничуть не помешает.

Просто устанавливаем LiteX, как указано в пояснении к проекту. Если Yosys/NextPNR я собирал под Windows при помощи серпа, молота и какой-то матери, то здесь единственная сложность была в установке утилиты PIP. Дальше LiteX прекрасно встал автоматически. Под Linux, наверняка, всё будет ещё проще. Дальше я запустил, согласно инструкции, сборку… И получил ошибку уже на этапе работы Yosys/NextPNR. Причём насчёт Линукса – не уверен. Заказчик собирал в нём и не говорил ни про какие ошибки. Так что я буду говорить только про свою ситуацию

Сейчас я знаю, что ошибка заключалась в том, что при требуемой тактовой частоте 125 МГц, достижима только 70. При этом на реальном железе проект работать будет, если его дособрать. Осматриваемся в каталоге проекта после того, как отработал штатный пакетный файл. Вот такой интересный каталог в нём появился:

Проходим по цепочке build->gateware и попадаем в сказку:

Да это же уже известный нам Верилоговский проект! LiteX сначала преобразует Питоновский код в verilog (в целом, может и в VHDL, но сегодня мы видим Verilog), а потом уже запускает штатную среду сборки для конкретной ПЛИС.

Итак, что у нас получилось в этом сказочном каталоге? Там есть файл с исходником colorlite.v и файл с описанием выводов и частот colorlite.lpf. У кого плата версии, отличной от 7.0, тому этот файл пригодится особенно. Хотя можно, конечно, добавить конфигурацию и в Питоновские файлы, но сегодня речь не о них. Если интересно – могу сделать про них отдельную статью. Только я заранее знаю, что не будет спроса.

Ох, и поизучал я эти файлы, когда стыковал проект verilog-ethernet с этой платой! Но сегодня речь не о том. Смотрим содержимое файла build_colorlite.bat (в Линуксе явно будет что-то другое, но я работал в Windows):

yosys -l colorlite.rpt colorlite.ys || exit /b

nextpnr-ecp5 —json colorlite.json —lpf colorlite.lpf —textcfg colorlite.config —25k —package CABGA256 —speed 6 —timing-allow-fail —seed 1 || exit /b

ecppack colorlite.config —svf colorlite.svf —bit colorlite.bit —bootaddr 0 || exit /b

Собственно, из-за ошибок, срабатывают эти exit-ы. Но ошибка «Недостижимая FMax», как я уже сказал, не фатальна. Я вынес пакетный файл на уровень основного каталога и переписал его так:

setlocal

PATH=C:cygwin64bin;%PATH%

PATH=D:LATICEyosys-master;%PATH%

PATH=D:LATICEnextpnr-masteroutbuildx64-Release;%PATH%

PATH=D:LATICEnextpnr-masteroutinstallx64-Releaselib;%PATH%

PATH=D:LATICEOpenOCD-20210729-0.11.0bin;%PATH%

cd .buildgateware

yosys -l colorlite.rpt colorlite.ys

nextpnr-ecp5 —json colorlite.json —lpf colorlite.lpf —textcfg colorlite.config —25k —package CABGA256 —speed 6 —timing-allow-fail —seed 1

ecppack colorlite.config —svf colorlite.svf —bit colorlite.bit —bootaddr 0

Теперь у меня проект собирается. «Прошиваю» я его вот таким bat-ником:

setlocal

PATH=C:cygwin64bin;%PATH%

PATH=D:LATICEOpenOCD-20210729-0.11.0bin;%PATH%

cd .buildgateware

openocd -f myConfig.cfg

Когда проект залит, все инструкции с Гитхаба начинают работать. То есть, я могу запустить Питоновский скрипт test_blink.py, который помигает светодиодом. Подробнее посмотрите в самих файлах с Гитхаба.

Суть работы этой системы похожа на ту, которую я активно продвигал в цикле лекций про наш комплекс Redd. LiteX позволяет построить процессорную систему с настоящим процессорным ядром (например, RISC-V) и настоящей шиной (например, Wishbone). К этой шине подключаются какие-то периферийные устройства. Одно из возможных устройств – переходник Ethernet-Wishbone. И никто не мешает нам не включать в эту систему сам процессор. Так у нас получается на шине Ethernet-овский мастер и блок GPIO, подключённый, в том числе, и к светодиоду. Обращаясь к порту, обслуживающему данный блок, мы можем управлять состоянием светодиода. Сложно? Ну да. Зато демонстрируются принципы работы с массой полезных в жизни узлов.

9 Заключение

Мы познакомились с методикой быстрого старта работ с ПЛИС фирмы Lattice. Особенность описанной методики в том, что она малозатратна как по финансам, так и по требуемому времени. Владение техникой работы с разными видами систем, полезно для программиста вообще, а в наше неспокойное время, когда с рынка исчезают самые популярные микросхемы, полезно вдвойне. Особо следует отметить, что рассмотренная среда разработки является не пропертиреарной, а открытой. Она бесплатна, поддерживается сообществом и может быть собрана из исходных кодов. Автору особо греет душу тот факт, что в результате сборки могут получиться полноценные Windows-приложения.