Любая комбинация софтвера и цифрового хардвера — от микроконтроллера, двигающего дворники у автомобиля — до серверной фермы с много-много-ядерными процессорами, аппаратными ускорителями ML и ChatGPT — сводятся к конечному автомату с достаточно большим состоянием. Независимо от сложности и адаптивности программ.

Простым примером конечного автомата является механический арифмометр, производящий умножение столбиком. Он получает информацию от человека через рычажки, у него есть аналог тактового сигнала — поворот ручки, который меняет состояние конечного автомата. Также у арифмометра есть функция преобразования текущего состояния в следующее и вывод информации через цифры. Все атрибуты Finite State Machine — FSM.

Сводится ли к конечному автомату человеческий интеллект? К сожалению, у человеческого интеллекта есть атрибут, природа которого современной науке неизвестна и который никогда не наблюдался у конечных автоматов. Этот атрибут — ощущение собственного «я», self-awareness. Конечно вы можете сделать в программе переменную «я_чувствую_собственное_я» и присвоить ей true, а потом утверждать, что вы симулируете собственное «я», но это жульничество, а не технология.

Я вовсе не пытаюсь нагонять мистику или агитировать за бога. Self-awareness наверняка такой же физический феномен, как какая-нибудь термоядерная реакция. Но скажем древние греки не знали природы термоядерной реакции. Наверное, они вели диалоги типа «если ты не веришь, что Солнце — просто большой костер из дров, то значит ты веришь в сказки про Зевса и других богов?»

Также вспомним, что древние греки считали, что человек думает сердцем, а мозг — только железа для охлаждения крови. А что — сердце же начинает сокращаться быстрее, когда мы волнуемся, не так ли?

Возможно, мы — те же самые древние греки по отношению к self-awareness. Кто знает — может быть self-awareness не только не конечный автомат, но еще и не особо привязана к нейронам. Типа там стоит какой-нибудь портал в пятьдесят второе измерение, где оно и происходит. И возможно, наука когда-нибудь разберется, что это такое. А может быть, и не разберется. Среднее время существования вида млекопитающего — всего миллион лет, у нас осталось всего несколько сот тысячелетий, чтобы разобраться с вопросом, и этих тысячелетий возможно и не хватит.

Может быть и так, что нашему виду Homo sapiens познать self-awareness просто не дано, как муравьям не дано построить ракету SpaceX и отправиться на ней на Марс.

Прежде чем обсудить, что же делать, ответим на еще один тезис: «А что если ощущение собственного «я» — просто иллюзия?«

Этот тезис выглядит как психзащита. Вспомним исторический курьез: с 1565 до 1815 год вдоль берега северной Калифорнии каждый год проплывал так называемый Манильский галеон, торговый корабль, следующий из Филиппин в Мексику. Он никогда не останавливался — купцы просто использовали быстрое прибрежное течение, чтобы пронестись вдоль берега на юг к Акапулько. При этом, берег северной Калифорнии был обитаем. На нем жили индейцы, которые не знали природы корабля, хотя он регулярно проплывал мимо на глазах у десятка поколений. Возможно старейшины утешали молодежь, что объект на горизонте — это просто иллюзия, а молодежь пыталась уговорить себя, что это просто большой тюлень.

Также есть школа мысли, что один арифмометр конечно не обладает self-awareness, но если заставить арифмометрами все планеты солнечной системы и соединить их рычажками с дополнительными шестеренками и обратными связями для адаптируемости, а также присоединить генераторы псевдослучайных чисел — то ощущение собственного «я» в такой конструкции как-то само по себе самозародится, как личинки мух в протухшем мясе.

Является ли такое представление научной гипотезой или квазирелигиозной верой? Если вы считаете, что это научная гипотеза, то предлагаю вам обсудить ее фальсифицируемость по Попперу. Если же нет, обсудим следущий вопрос:

Что делать?

Решение я нашел в книжке советского писателя Владимира Сорокина «Тридцатая любовь Марины». Главная героиня книги проводила время с гуманитариями, диссидентами и фарцовщиками, отчего была постоянно несчастна. Но однажды с нею приключилось чудо. Марина встретила секретаря парткома завода Сергея Румянцева, который подарил ей простое женское счастье. После чего Марина устроилась на завод компрессоров расточницей и ее страдания тут же прекратились.

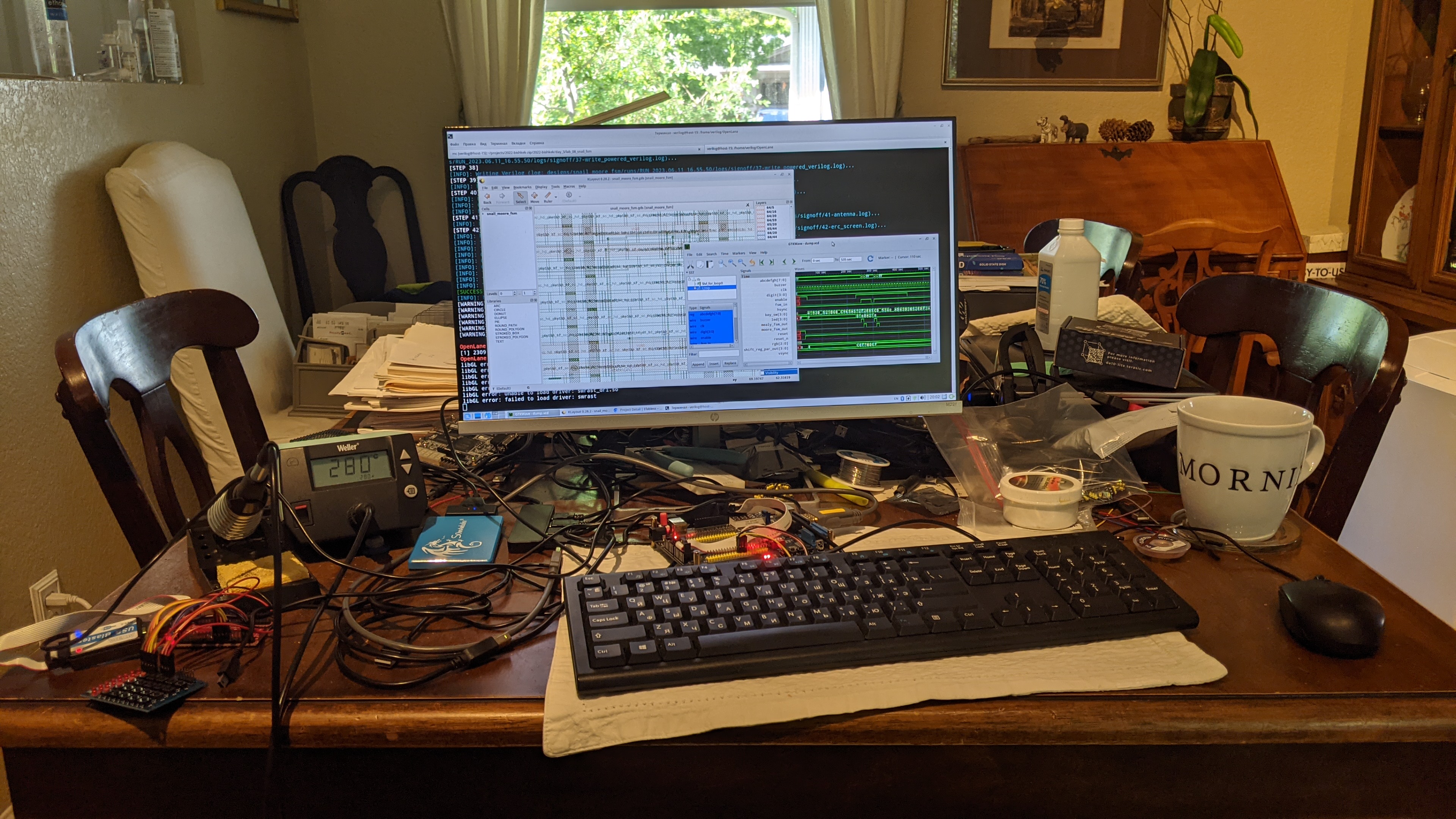

Я это все к чему: самый простой способ достичь счастья — это бросить споры об искуственном интеллекте и сингулярности, и заняться чем-нибудь практическим, с понятным результатом. Не обязательно стоять за станком. Можно проектировать микросхемы для телефонов и сетевых машрутизаторов, ну или на худой конец микроконтроллеры для той же ракеты на Марс. Но чтобы это делать, нужно твердо овладеть навыками проектирования микроархитектуры на уровне регистровых передач. Об этом пойдет речь на семинаре LaLambda в Грузии, который состоится 15-23 июля. LaLambda — это такое мероприятие, которое начиналось с обсуждения формальных методов и автоматического доказательств теорем, но сейчас впитало в себя функциональное программирование, хаскели и лиспы, ML (куда же без него?), статический анализ программ, йогу, музыку и танцы, и вот теперь — железо.

Вот мое превью для семинара:

Как цифровые схемы реализуют алгоритмы и почему специализированный ASIC на порядки быстрее CPU

Программирование настолько сильно завязано на семантику фон-Неймановской машины, что многим просто не приходит в голову, что алгоритмы можно реализовывать не в виде цепочек инструкций. И не в виде их вариаций: многоядерных кластеров с несколькими цепочками или микрокода, с последовательной генерацией контрольных сигналов из цепочки квази-инструкций с ветвлениями в памяти.

На самом деле CPU и все его варианты — это очень частный случай того, что можно сделать в хардвере. Для того, чтобы понять, что можно сделать в хардвере, на него нужно смотреть не в терминах программирования (циклы, вызовы функций итд), а в других, аппаратных терминах: комбинационное облако и элементы состояния, конвейеры и очереди, такты и задержки внутри такта, определяющие тактовую частоту.

В последние 30 лет проектировщики микросхем не рисуют цифровые схемы мышкой на экране, а синтезируют их кода на языках описания аппаратуры Verilog и VHDL. Этот код внешне поход на программы, но имеет другую семантику, которую мы и покажем в этом курсе. Кроме выполнения кода на симуляторе, код в целях обучения полезно синтезировать, превратить в граф из логических элементов, и прошить в память специализированных микросхем, которые называются FPGA.

FPGA — это матрица из ячеек с изменяемой логической функцией. Внутри них них можно строить цифровые схемы, в том числе схемы процессоров. Хотя FPGA менее эффективные, чем фиксированные микросхемы, которые изготавливают на фабрике, в проектировании для FPGA используются те же языки описания аппаратуры. Кроме этого, в них, в отличие от симулятора, в FPGA есть физические задержки внутри такта, поэтому если ваш дизайн вылезет за бюджет, определяемый тактовой частотой, схема будет глючить, и вы наглядно это увидите.

Помимо элементарных лаб с FPGA мы покажем как строить простейший процессор, а также как применять FPGA для обработки звука. Мы также пройдем через использование открытого пакета Open Lane, который используют исследователи для проектирования ASIC-ов как альтернативу коммерческим пакетам от Synopsys и Cadence.

И наконец, мы соединим другие темы LaLambda, формальные методы и решатели ограничений, с применениями в электронных компаниях. В которых доказательства утвердждений темпоральной логики применяются для верификации конвейеров, а решатели ограничений применяются для генерации непротиворечивых псевдослучайных транзакций в функциональной верификации во время симуляции.

И еще некоторые заметки, что там будет:

Лекция 1: Маршрут проектирования современных микросхем с высоты птичьего полета

Первые микросхемы начала 1970-х годов проектировались карандашом на бумаге или склеиванием кусков цветного картона. Затем появились программы для автоматического размещения компонент, схему из которых проектировщик рисовал мышкой на экране. В конце 1980-х — начале 1990-х годов возник современный машрут проектирования, при котором схема синтезируется из кода на языке описания аппаратуры. Это позволило радикально повысить производительность труда проектировщика и привело к современному миру с смартфонами и ускорителями ML.

Помимо описания маршрута проектирования CPU, GPU и сетевых чипов мы поговорим про цикл разработки микросхем, организацию труда в команде. Чтобы понять, как выглядит работа проектировщика, мы смоделируем, а затем синтезируем простой процессор, определим его максимальную тактовую частоту и размеры на кристалле. Для практического упражнения мы воспользуемся открытыми средствами проектирования: Icarus Verilog для симуляции на уровне регистровых передач и Open Lane для синтеза, размещения и трассировки. Мы увидим окончательный образ фотошаблона нашего процессора с помощью программы klayout.

Лекция 2: Какими объектами манипулирует микроархитектор блока цифровой микросхемы для организации потока вычислений?

Когда программист пишет скажем компилятор, он не мыслит в терминах операторов «if» и циклов «while». Он мыслит алгоритмами типа обхода деревьев выражений. Точно так же микроархитектор аппаратного блока мыслит не элементарными элементами И/ИЛИ/НЕ, а более крупными объектами: стадиями конвейера, очередями FIFO, конечными автоматами, а также арбитрами для разделения доступа к вычислительным FPU и блокам быстрой памяти, расставленными внутри микросхемы.

С помощью таких примитивов можно строить структуры, которые обрабатывают сетевые пакеты или потоки цветных треугольников для компьютерной графики на два-три порядка быстрее, чем это возможно с помощью традиционного CPU, пусть даже многоядерного.

Во время лекции мы рассмотрим как вид таких структур на высоком уровне микроархитектурных диаграмм, так и их реализацию на языках описания аппаратуры, на уровне регистровых передач.

Лекция 3: Формальные методы при верификации цифровых микросхем в электронных компаниях

Двадцать лет назад электронная промышленность относилась к формальным методам со скепсисом. Матерые контракторы, проектирующие конвейеры для графики и сетевых чипов называли программы для формального доказательства утверждений о свойствах электронных схем — игрушками.

Но прошло время, и программы типа Cadence Jasper Gold и Synopsys VC Formal вошли в обиход. Они позволяют доказывать (или опровергать) утверждения так называемой темпоральной логики, выраженные с помощью так называемых SystemVerilog Assertions (SVA).

Пример такого утверждения: «если через два такта после сигнала A-верно появится сигнал B-верно, и сигнал STALL во время всей последовательности будет оставаться нулем, то через три такта на выходе D возникнет результат вычислений A и B». С помощью формальных методов можно находить очень редкие случаи в аппаратных конвейерах, которые не возникнут за месяцы работы симулятора.

Это не нечто академически-абстрактное, а квалификация ведущая к конкретной работе с зарплатой. Вот объявление выставленное сегодня:

Лекция 4. Решатели ограничений при верификации цифровых микросхем в электронных компаниях

Лавинообразный рост размеров и возможностей микросхем в 1990-е годы привел к проблеме, которую менеджеры проектов описывали так: «мы можем многое спроектировать, но не можем это все верифицировать». В те времена микросхемы верифицировали написанием большого количества тестов на частные случаи.

Появилось несколько стартапов в области верификации (Verisity, System Science и другие), которые построили схему верификации, при которой один инженер генерирует ограниченно-псевдослучайные транзакции к устройству, а другой инженер проверяет, что среди этого потока встретились все интересные сценарии, прописанные в плане тестирования.

По английски это тандем называется functional-coverage driven constrained-random verification. Для него в языке SystemVerilog появились два подъязыка — один для формулировки ограничений (constraints), другой для распознавания комбинаций сигналов (functional coverage groups).

Интересной чертой языка органичений является его двунаправленность. Например если задать ограничение «из a < 2 следует что b > 3″, то при последующей попытке установить «b == -1» решатель никогда не сгенерит например «a == 1», так как такое значение «a» будет противоречить ограничению. То есть «if» будет работать задом наперед, не как в императивных языках программирования.

Обычно решатели ограничений используются для генерации транзакций на шине типа AXI, но мы попробуем необычное использование — для генерации случайных, но при этом корректных инструкций архитектуры RISC-V. В случае генерации инструкций можно задать отношения между разными полями и закодированной инструкцией, после чего наложить ограничения на поля — и решатель будет генерировать инструкции. А можно сделать наоборот — зафиксировать закодированную инструкцию и дать решателю ограничений разложить ее на поля, то есть реализовать на решателе ограничений дизассемблер.

Занятие 5. Распознавание нот и мелодий аппаратной схемой на FPGA, без софтвера, без процессора и даже без алгоритмов DSP

Распознавание нот и мелодий — полезное упражнение для тех, кто только основил основы проектирования на уровне регистровых передач. Мы устанавливаем период синусоиды уровня звука из микрофона, просто подсчитывая количество тактов 50-мегагерцового тактового сигнала между двумя пересечениями уровня некоторого порога. Далее мы реализуем конечный автомат (точнее, сразу несколько конечных автоматов, работающих параллельно), которые определяют популярные мелодии.

Во время занятия Мария Беличенко будет играть живые мелодии концертной флейтой Бёма. С одной стороны, флейта дает очень чистую синусоиду, но с другой стороны, это живой звук, который нужно фильтровать. Мы могли бы производить и звуки генератором из телефона, но это было бы неспортивно.

Кроме этого, мы собираемся привезти и раздать участникам 20 блокфлейт, на которых гораздо проще научиться играть простые мелодии, чем на поперечной концертной флейте. Мария обучит желающих, как это делать, и участники смогут тестировать качество обработки звука на FPGA, используя в качестве источника собственную игру на блокфлейте.

В конце семинаров мы проведем хакатон, на котором участники попробуют не только распознавать, но и генерировать звуки с помощью FPGA платы и усилителей: играть мелодию в ответ, играть мелодию в другой тональности итд.

Так что Гамарджоба в Тбилиси, присоединяйтесь!