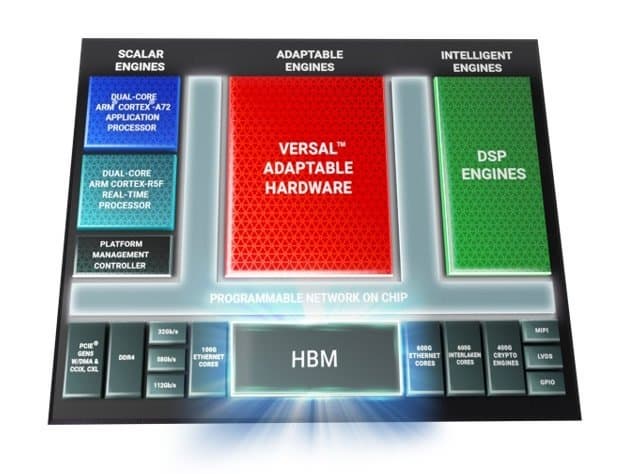

Компания Xilinx представила платформу адаптивного ускорения вычислений Versal HBM (ACAP), новейшую серию в портфолио Versal. По словам производителя, серия Versal HBM «обеспечивает конвергенцию быстрой памяти, безопасного подключения и адаптируемых вычислений на одной платформе». Конфигурация Versal HBM ACAP включает самую передовую память HBM2e DRAM, позволяющую получить объем 32 ГБ и пропускную способность 820 ГБ/с — в восемь раз больше, чем у памяти DDR5. При этом энергопотребление получается на 63% ниже, чем в решениях с DDR5. Как утверждается, серия Versal HBM спроектирована таким образом, чтобы удовлетворять повышенные потребности в памяти наиболее ресурсоемких приложений для центров обработки данных, проводных сетей, тестового и измерительного оборудования, а также для аэрокосмической и оборонной промышленности.

К достоинствам Versal HBM отнесены IP-ядра ввода-вывода с высокой пропускной способностью, включая приемопередатчики PAM4, Ethernet, Interlaken и PCIe Gen5 со встроенным механизмом DMA, поддерживающим CC и CXL. Этот широкий набор предопределенных IP-ядер обеспечивает готовое подключение с поддержкой широкого спектра протоколов, скоростей передачи данных и стандартов. Будучи оптимизирован по производительности и энергопотреблению, он способствует сокращению времени разработки и выхода на рынок.

Микросхемы Versal HBM рассчитаны на выпуск по нормам 7 нм. Разработчики могут начать создание прототипов с использованием микросхем и плат серии Versal Premium и легко перейти на серию Versal HBM, когда она станет доступна. Ознакомительные образцы Versal HBM должны появиться в первой половине 2022 года. Документация доступна уже сейчас, а инструменты для разработчиков станут доступны в рамках программы раннего доступа в текущем полугодии.

Источник: iXBT