Я уже рассказывал про молодоженов Владислава и Елены Шаршиных, который вместе с их коллегой Андреем Папушиным компания Intel привезла в Калифорнию за серебряную победу на конкурсе InnovateFPGA. Их интервью есть в недавно вышедшем лабнике «Цифровой синтез». Этот лабник мы собираемся использовать на семинаре для школьников и младших студентов, который пройдет 15-17 сентября на выставке ChipEXPO в Сколково. Если вы собираетесть повторить (или превысить) достижение Шаршиных и Папушина, или просто стать FPGA или ASIC designer-ом, не выезжая в Санта-Клару, то участие в семинаре, или даже просто просмотр начальных инструкций в этом посте — поможет вам начать.

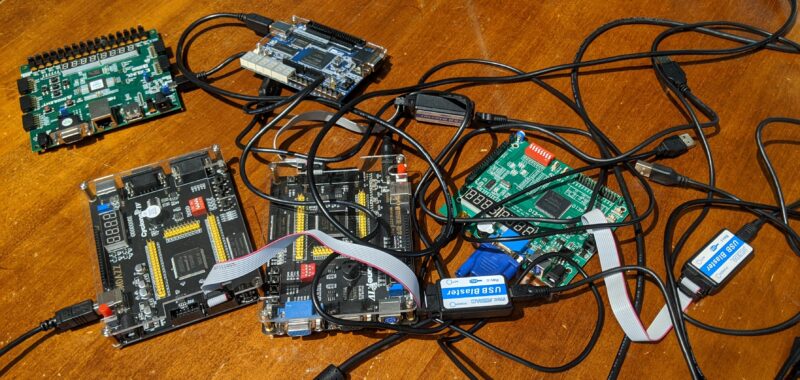

Многие из зарегистрировавшихся на семинар уже получили FPGA платы (их раздачей занимается образовательное отделение РОСНАНО) за прохождение теоретического пререквизита. Теперь было бы очень желательно, если бы участники семинара заранее установили Intel FPGA Quartus (или, если кто-нибудь не любит Intel / Altera, то Xilinx Vivado), и запустил на нем хотя-бы примитивный тест. Даже не мигание LED, а вообще один логический элемент XOR. Если все это сделают заранее, то на семинаре мы будем обсуждать не тривиальные проблемы типа «у меня драйвер для USB Blaster не находится», а что-нибудь поинтереснее, например что спрашивают на интервью на позицию RTL Logic Designer-а в NVidia, AMD, Apple и другие компании.

Итак, прежде всего у семинара есть организация на гитхабе. Вы можете клонировать отуда репозиторию ce2020labs и использовать файлы из директории before для проверки вашей платы, установки Quartus или Vivado, драйверов и решении проблемм с программатором. В директории есть файлы для семи плат: пять плат с Intel FPGA (два варианта OMDAZZ / rzrd, два варианта ZEOWAA и Terasic DE10-Lite), и две платы с Xilinx (Basys3 и Nexys4).

Если вы не хотите пользоваться GitHub-ом, вы можете просто скачать zip отсюда. Все эти файлы будут работать и с версиями Quartus и Vivado под Windows, и под Linux.

Для установки Quartus-а вы можете посмотреть детальное видео от Сергея Иванца, декана факультета электронных и информационных технологий Черниговского национального технологического университета:

Видео:

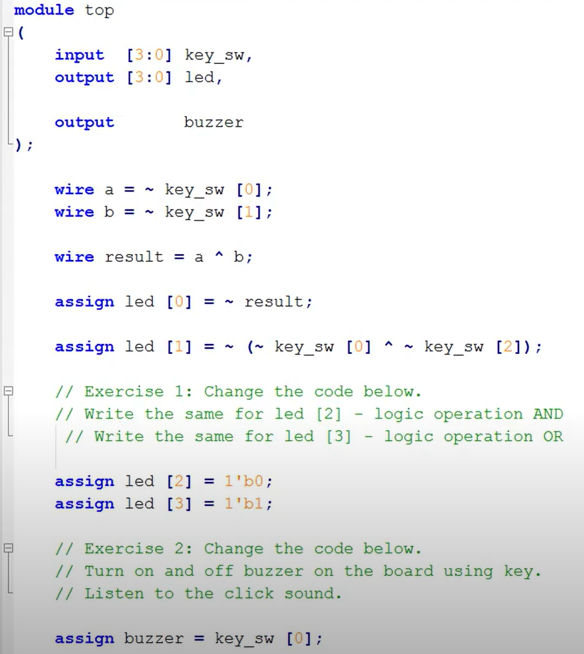

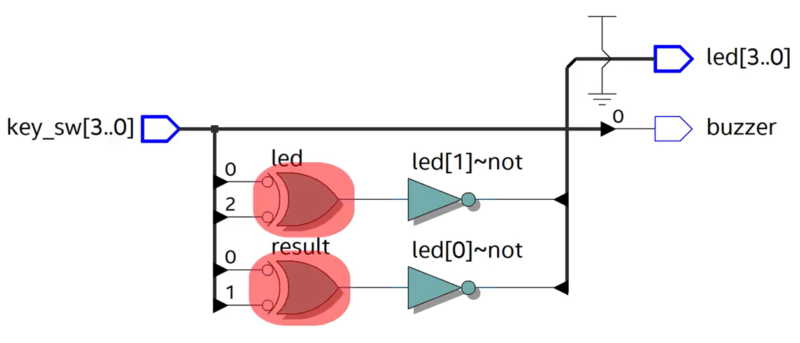

И видео по синтезу простейшего примера из описания на языке Verilog:

С детальным описанием что к чему:

Единственная проблема — в этом видео не очень хорошо раскрыто использование программатора (и проблемы с его драйверами). Поэтому вам может оказаться полезным посмотреть другое видео, тоже от Сергея, где он описывает использование USB Blaster после редактора схематики. Тут надо сказать, что schematic entry вышло из употребления проектировщиков цифровой микроэлектроники в начале 1990-х (все перешли на проектирование с помощью языков описания аппаратуры Verilog и VHDL), но Сергей все-таки решил показать это чисто чтобы начинающий заниматься цифровым проектированием студент сразу интуитивно понял, что мы проектируем схемы, а не пишем программы, хоть код на верилоге и похож на код на языке программирования.

Вот видео с schematic entry, в конце которого расписано использование программатора:

До, во время и после семинара на ChipEXPO в Сколково мы будем продолжать выкладывать разные материалы, но чтобы посмотреть все (в том числе например мини-лекцию, как организованы команды по разработке чипов в Silicon Valley) — лучше зарегистрироваться.

_large.jpg)