Корпорация Advanced Micro Devices планирует поставить образцы процессоров на базе микроархитектуры Zen ряду клиентов уже в текущем квартале. В компании не указывают принадлежность устройств, однако сам анонс говорит о том, что AMD располагает работающими CPU на базе микроархитектуры Zen.

«Мы довольны прогрессом Zen», — сказала Лиза Су (Lisa Su), исполнительный директор и президент AMD, в ходе телеконференции с инвесторами и финансовыми аналитиками. «Очевидно, что существует множество инженерных этапов, которые требуется пройти, но ключевым фактом является то, что мы поставим [образцы изделий] нашим приоритетным клиентам во втором квартале».

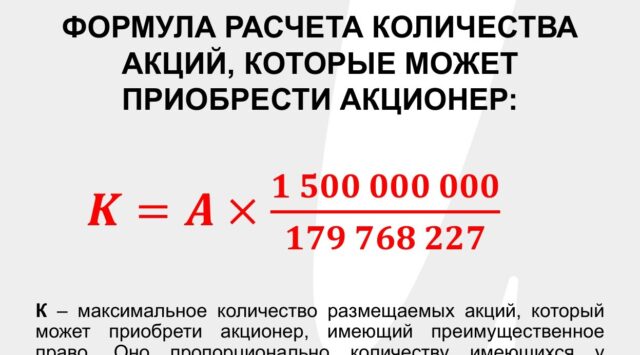

Ожидаемая относительная производительность CPU на базе Zen

Согласно заявлению госпожи Су от июня 2015 года (касающихся отправки цифрового проекта неизвестного CPU на основе FinFET-транзисторов производителю), компания должна была получить образцы осенью прошлого года. AMD подтвердила наличие работающих процессоров на базе микроархитектуры Zen в октябре. Кроме того, в октябре AMD и GlobalFoundries раскрыли тот факт, что эти устройства производятся по технологии 14 LPP.

Если верить неофициальным данным, раскрытым одним из китайских сайтов в середине прошлого года, образцы CPU на базе микроархитектуры Zen в статусе ES (enginering sample) должны были быть получены клиентами AMD в апреле этого года. Лиза Су подтвердила факт поставки клиентам (косвенно подтвердив наличие работающих CPU на основе Zen в лабораториях компании). Вопрос о статусе процессоров на базе микроархитектуры Zen, которые были отправлены клиентам AMD, остался без ответа в пятницу.

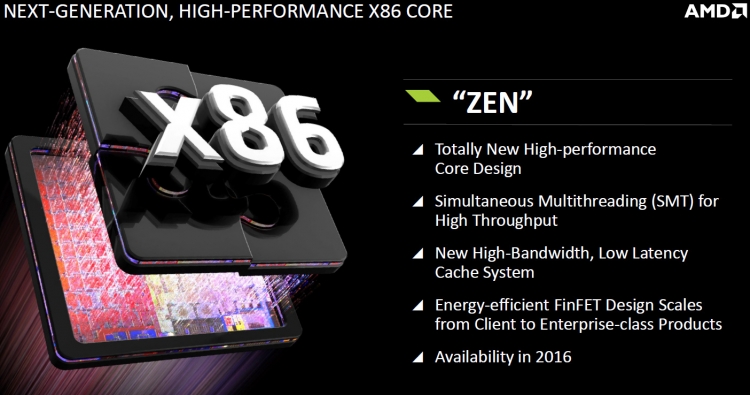

Некоторые особенности микроархитектуры AMD Zen

«С точки зрения рынков, к которым мы собираемся обратиться [c CPU на базе Zen], мы считаем, что [микроархитектура] Zen принесёт пользу [для серверов]», — сказала госпожа Су. «Мы будем продолжать работать с OEM и ODM-производителями, чтобы гарантировать, что они имеют [работающие материнские платы] для нашей продукции».

Согласно неофициальным данным, первые процессоры на базе микроархитектуры Zen имеют восемь ядер и двухканальный контроллер памяти DDR4. Серверные модели могут иметь большее количество ядер и интерфейсов работы с памятью.

Источник: